## Introduction & Motivation

CPEN 230 – Introduction to Digital Logic

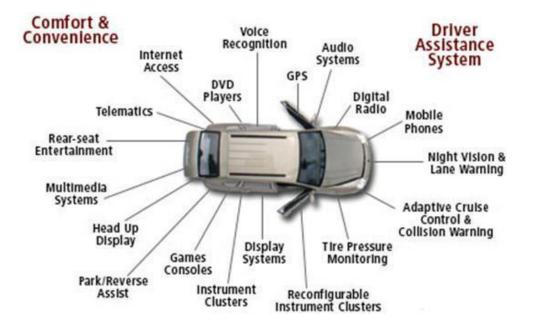

### **Common Applications**

- Desktop Computers

- Notebooks

- Smartphones

- Embedded Systems

CPEN 230 Digital Logic

CPEN 231 Microcontrollers

> CPEN 342 Embedded Systems

CPEN/CPSC 431 Computer Architecture EENG 406 Integrated Circuits

CPEN 430 Digital Systems Design EENG 412 Digital Controls

EENG 422 Digital Communications

> EENG 424 Digital Signal Processing

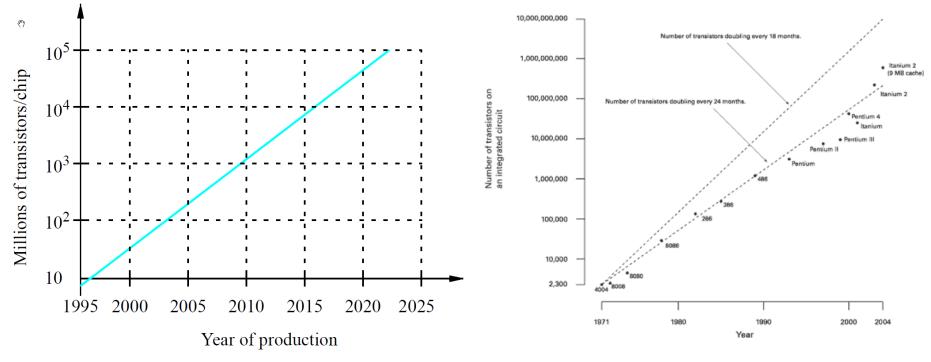

#### Moore's Law

An estimate of the maximum number of transistors per chip over time.

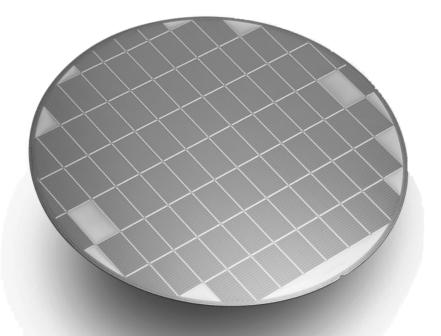

### Enabling Technology

A silicon wafer (courtesy of Altera Corp.).

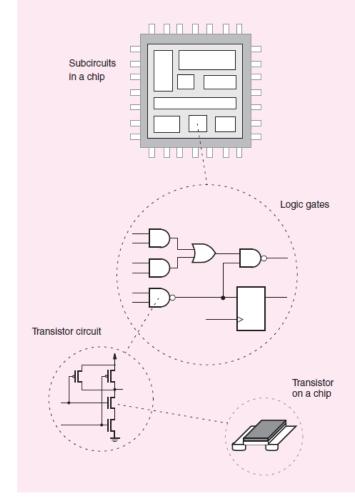

The focus of this class is on digital circuits: i.e. the interconnection of logic gates

An example of chip (CPU)

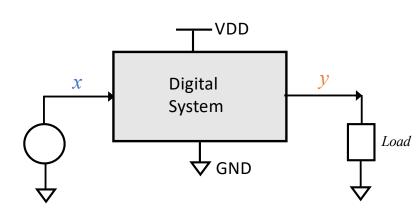

Figure 1.4 A digital hardware system (Part b).

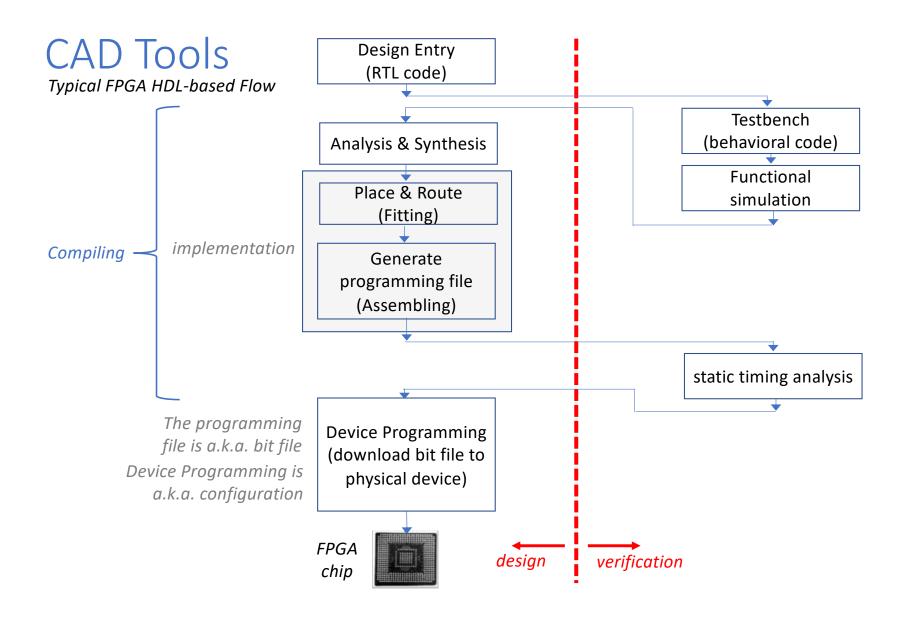

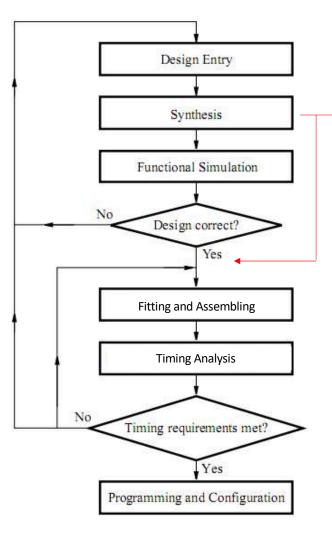

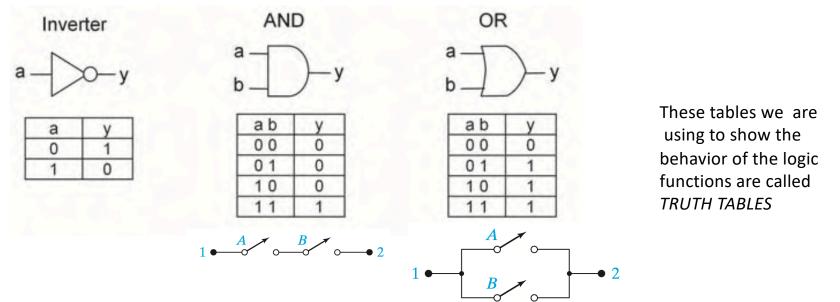

#### The flow is iterative!

Unless you don't You don't trust your HDL coding skills you should first check that the functional simulation is correct and later run the synthesis

Figure 1. Typical CAD flow.

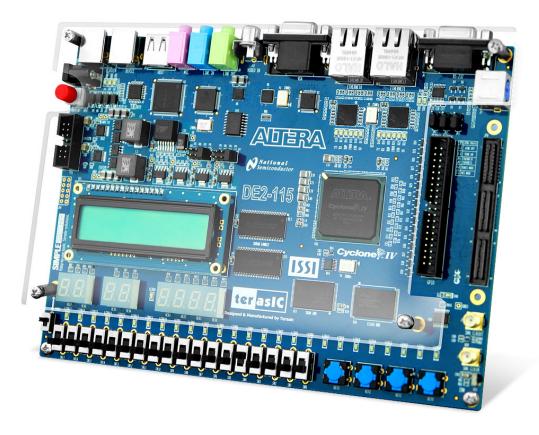

#### An FPGA (Field Programmable Gate Array) board.

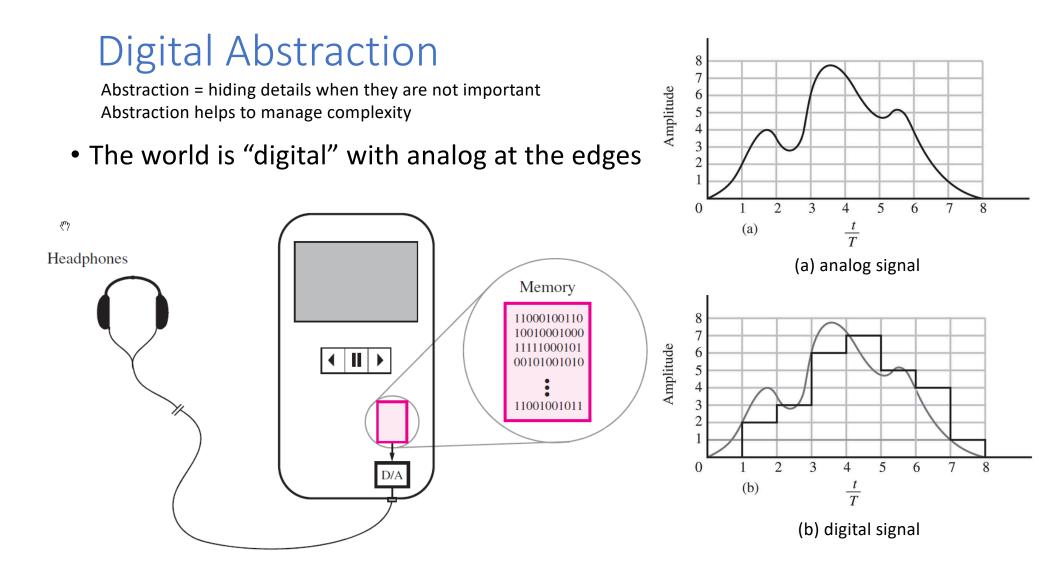

#### **Digital Abstraction**

Key idea:

assume we have only two voltage levels

- (i.e., assume binary signals)

- VDD <--> 1 <--> H

- GND <--> 0 <--> L

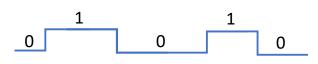

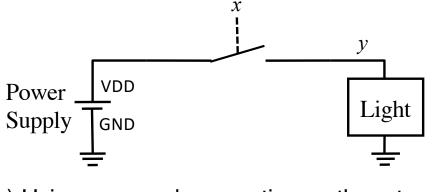

#### **Binary Waveforms**

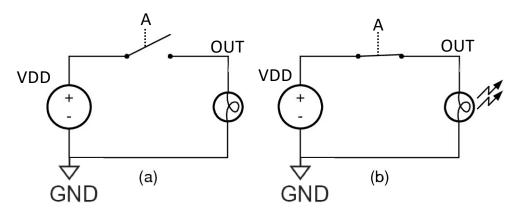

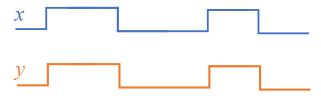

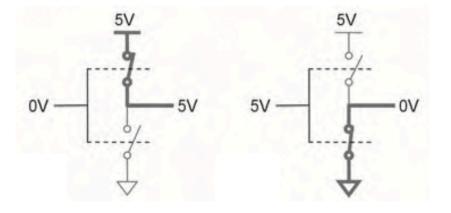

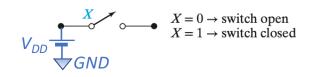

Assume we have a switch that when the control signal x is at VDD (x=1) the switch closes and when x is at GND (x=0) the switch opens

(a) Simple connection to a battery

х

V

Light

(b) Using a ground connection as the return path

#### Binary digits (bits)

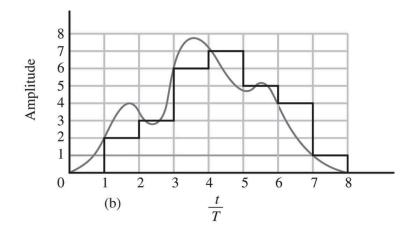

If we "slice" the amplitude of our analog signal in 8 values, we need 3 binary signals (i.e. 3 bits) to represent it ( $8 = 2^3$ ).

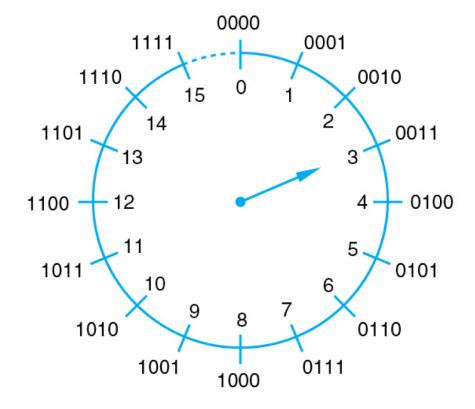

| Decimal | Binary |  |  |

|---------|--------|--|--|

| number  | code   |  |  |

| 0       | 0000   |  |  |

| 1       | 0001   |  |  |

| 2       | 0010   |  |  |

| 3       | 0011   |  |  |

| 4       | 0100   |  |  |

| 5       | 0101   |  |  |

| 6       | 0110   |  |  |

| 7       | 0111   |  |  |

| 8       | 1000   |  |  |

| 9       | 1001   |  |  |

| 10      | 1010   |  |  |

| 11      | 1011   |  |  |

| 12      | 1100   |  |  |

| 13      | 1101   |  |  |

| 14      | 1110   |  |  |

| 15      | 1111   |  |  |

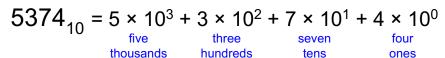

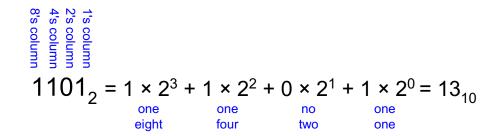

#### Number Systems

1's column 10's column 100's column

1000's column

# $num = \sum_{k=0}^{N-1} d_k R^k$

#### **Decimal numbers**

**Binary numbers**

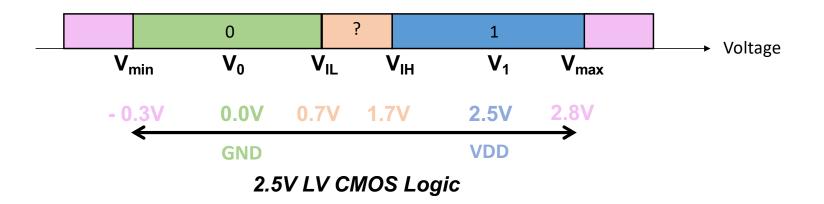

### Digital Abstraction: Voltage ranges of binary signals

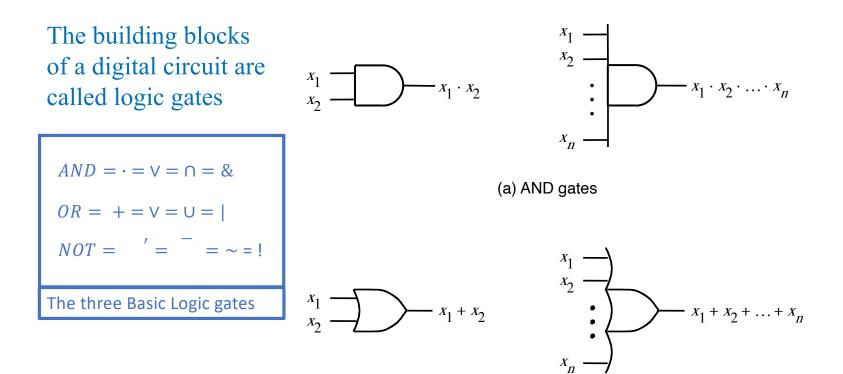

A digital circuit is a "network" of logic gates (i.e. a bunch of logic gates wired together)

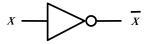

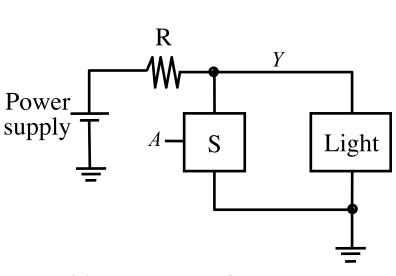

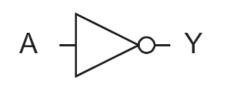

(c) NOT gate

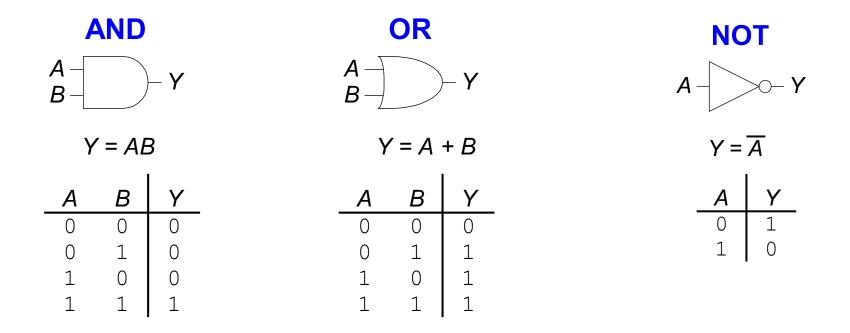

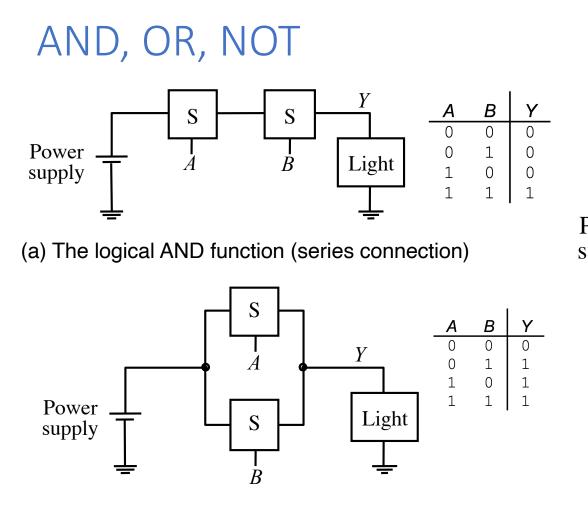

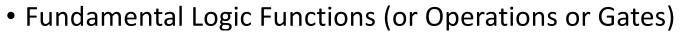

#### The Basic Logic Gates: AND, OR, NOT

These three basic components are all you need to build any possible logic circuit you want

(b) The logical OR function (parallel connection)

(c) The logical NOT function

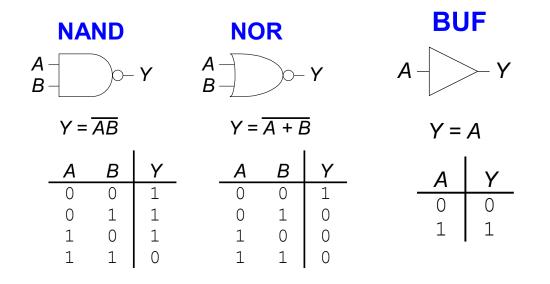

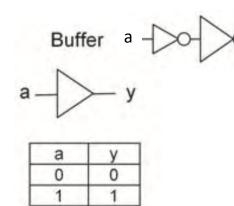

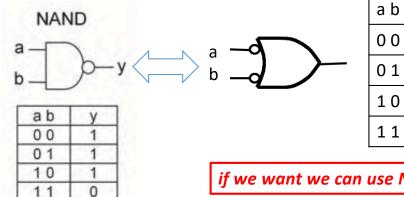

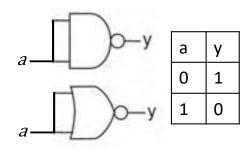

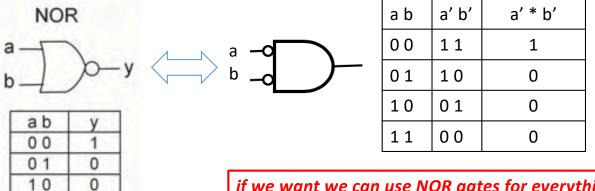

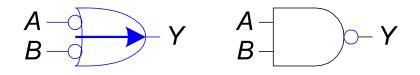

# More Logic Gates: NAND, NOR, and BUFFER (inverting AND, OR, and NOT)

It turns out that instead of using the three basic gates (AND, OR, NOT) you can build any logic circuit you want also by using only NAND gates or only NOR gates

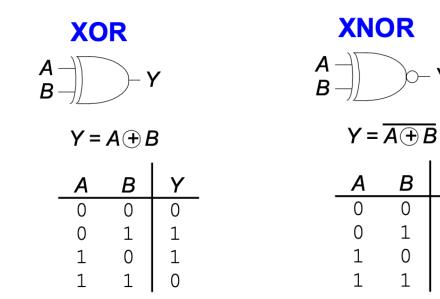

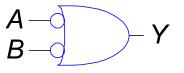

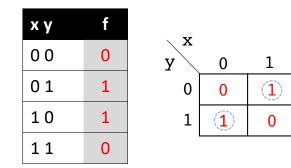

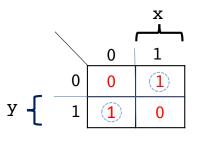

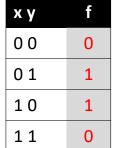

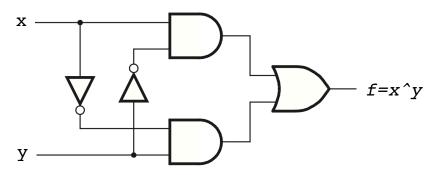

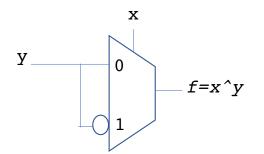

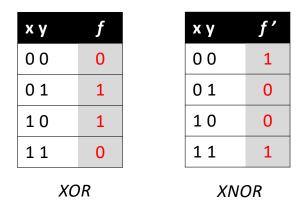

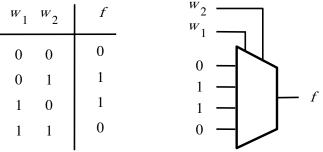

#### More Logic Gates: XOR, XNOR

- Y

Y

1

0

0

1

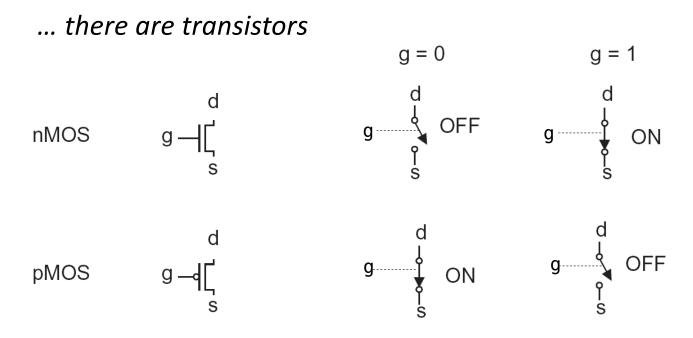

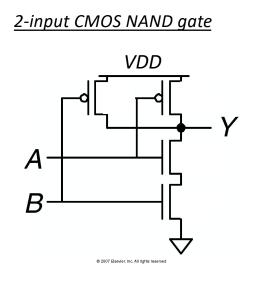

#### Beneath the Digital Abstraction

(a)

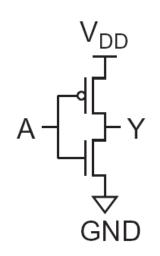

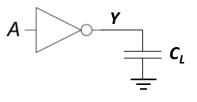

FIGURE 1.11 Inverter schematic (a) and symbol (b)  $Y = \overline{A}$

(b)

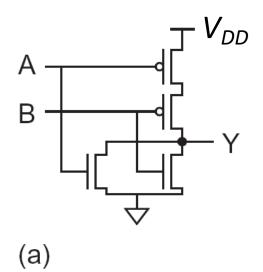

(a)

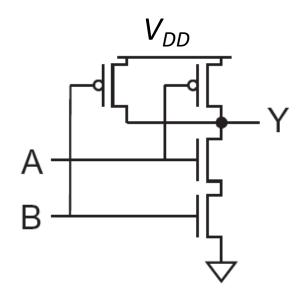

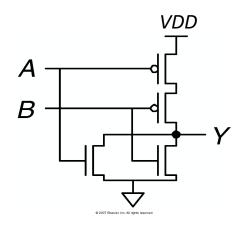

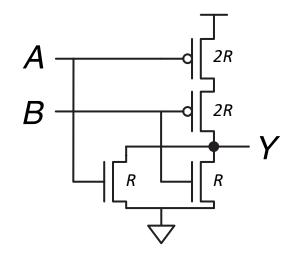

**FIGURE 1.12** 2-input NAND gate schematic (a) and symbol (b)  $Y = \overline{A \cdot B}$

**FIGURE 1.16** 2-input NOR gate schematic (a) and symbol (b)  $Y = \overline{A + B}$

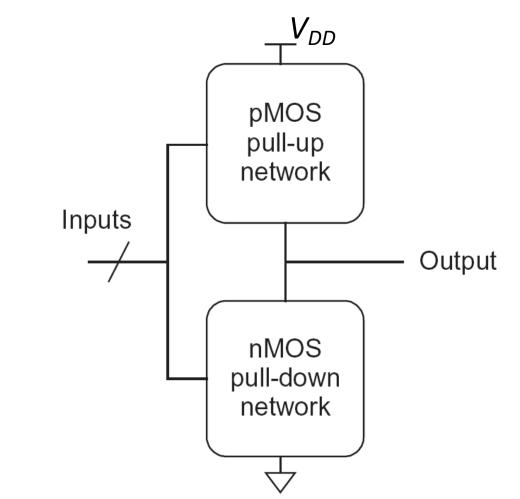

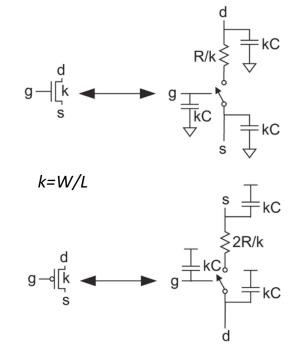

#### General CMOS Logic Gate

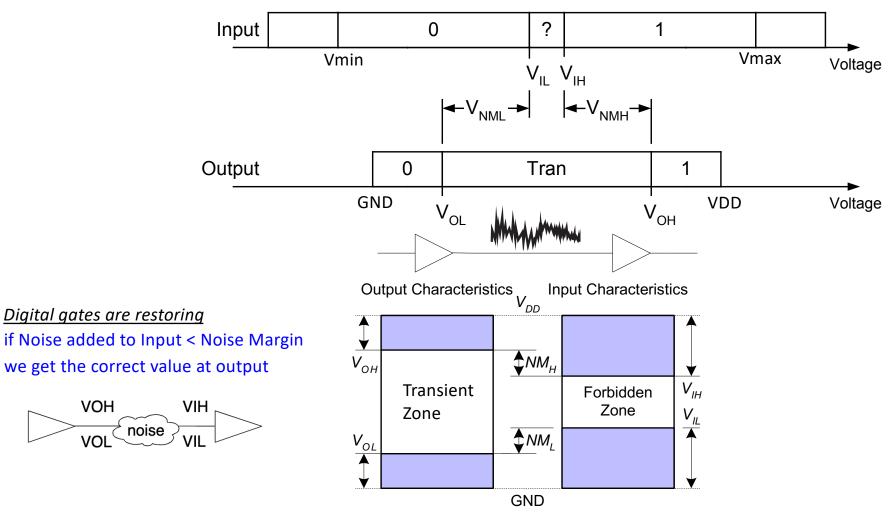

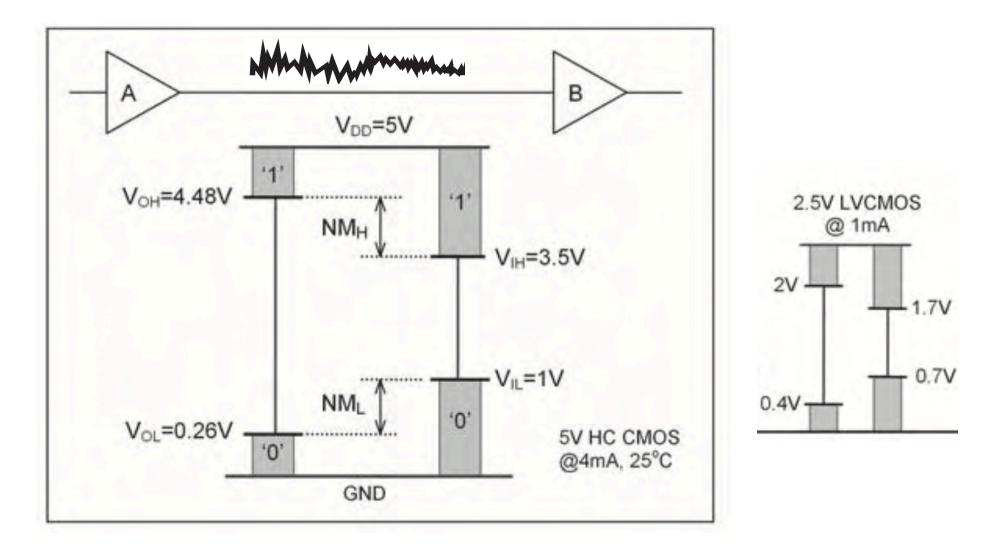

#### Logic Levels and Noise Margins

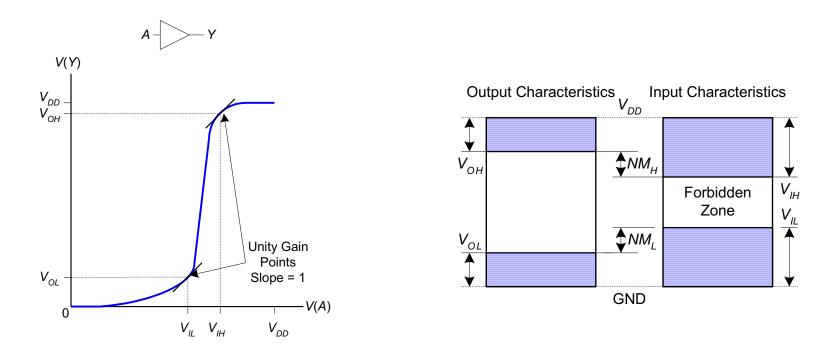

#### DC Transfer Characteristics

If gain < 1 the noise superimposed to a given level gets "attenuated"

#### **VDD** Scaling

- In 1970's and 1980's,  $V_{DD}$  = 5 V

- $V_{DD}$  has dropped

- Save power

$$P_d = \alpha \cdot C_L \cdot f_{clk} \cdot V_{DD}^2$$

- 3.3 V, 2.5 V, 1.8 V, 1.5 V, 1.2 V, 1.0 V, ...

- Be careful connecting chips with different supply voltages

## Logic Family Examples

| Logic Family | V <sub>DD</sub> | V <sub>IL</sub> | V <sub>IH</sub> | V <sub>OL</sub> | V <sub>OH</sub> |

|--------------|-----------------|-----------------|-----------------|-----------------|-----------------|

| TTL          | 5 (4.75 - 5.25) | 0.8             | 2.0             | 0.4             | 2.4             |

| CMOS         | 5 (4.5 - 6)     | 1.35            | 3.15            | 0.33            | 3.84            |

| LVTTL        | 3.3 (3 - 3.6)   | 0.8             | 2.0             | 0.4             | 2.4             |

| LVCMOS       | 3.3 (3 - 3.6)   | 0.9             | 1.8             | 0.36            | 2.7             |

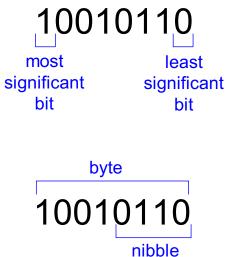

#### Bits, Bytes, Nibbles, Words, ...

Bits

Bytes & Nibbles

Bytes

most significant byte least significant byte ??

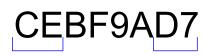

#### Hexadecimal Numbers

| Hex Digit | Decimal Equivalent | Binary Equivalent |

|-----------|--------------------|-------------------|

| 0         | 0                  | 0000              |

| 1         | 1                  | 0001              |

| 2         | 2                  | 0010              |

| 3         | 3                  | 0011              |

| 4         | 4                  | 0100              |

| 5         | 5                  | 0101              |

| 6         | 6                  | 0110              |

| 7         | 7                  | 0111              |

| 8         | 8                  | 1000              |

| 9         | 9                  | 1001              |

| А         | 10                 | 1010              |

| В         | 11                 | 1011              |

| С         | 12                 | 1100              |

| D         | 13                 | 1101              |

| Е         | 14                 | 1110              |

| F         | 15                 | 1111              |

#### Next Time

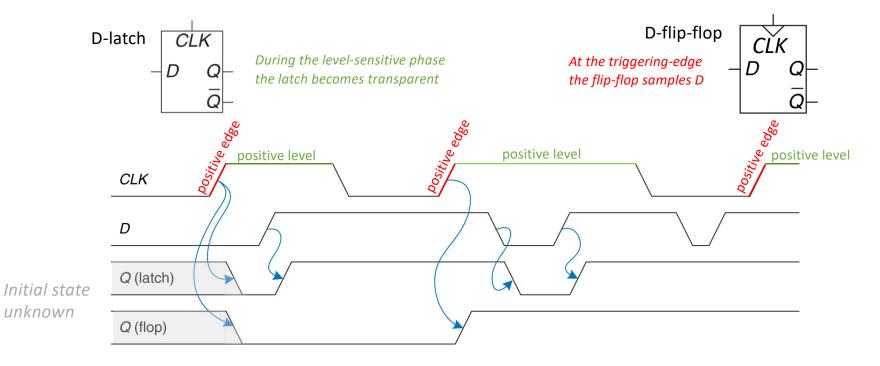

- Types of logic circuits: combinational circuits vs. sequential circuits

- Types of Integrated Circuits (ICs)

- Boolean Algebra

Combinational --> NOT Combinatorial

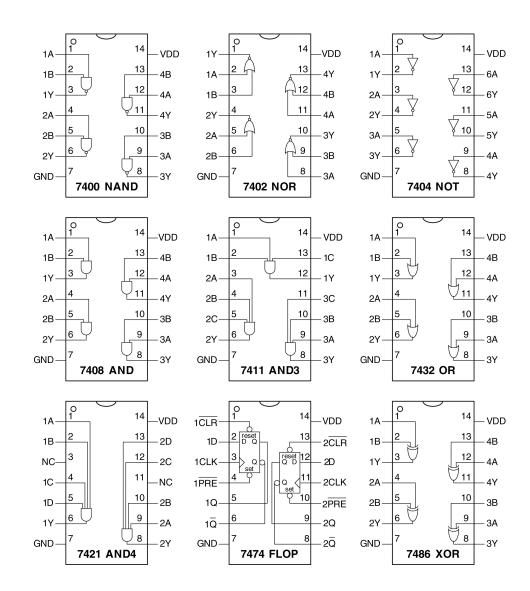

#### Common 74xx-series logic gates

## Boolean Algebra

CPEN 230 – Introduction to Digital Logic

#### Review

x

2

• Binary (or Boolean or Digital or Logic) Signal (or Variable)

### Review

#### Precedence of basic operations:

- Parenthesis

- NOT

- AND

- OR

A typical CAD Flow

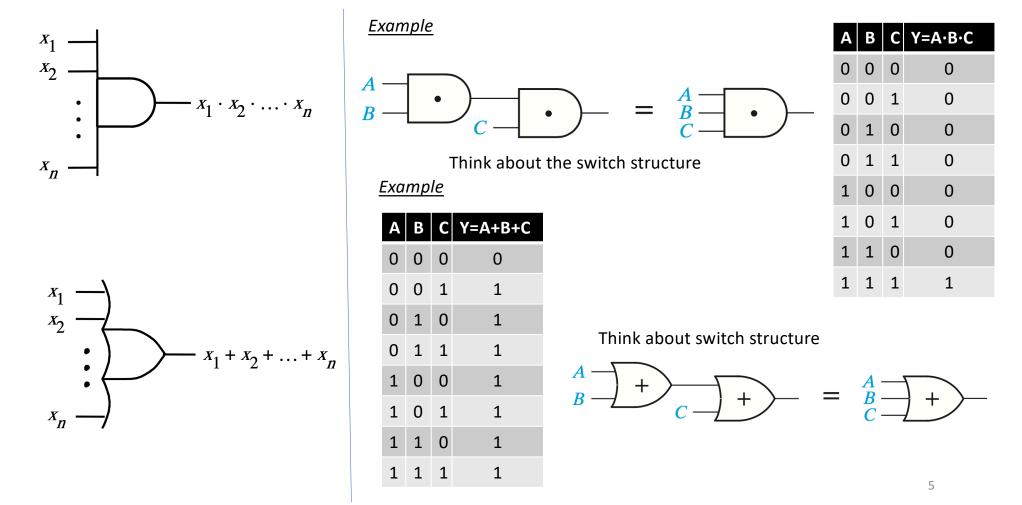

### AND and OR gates can have more than two inputs

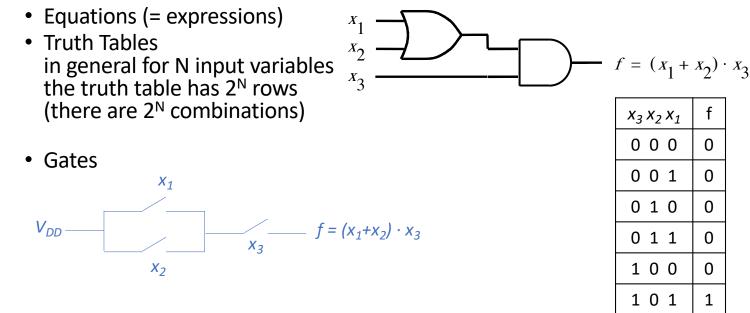

### "Composite" Boolean Functions (or Expressions)

• All Boolean Functions are formed by applying the basic operations to one or more variables or constants

| Α | В | С | Y=A⋅B′+C |

|---|---|---|----------|

| 0 | 0 | 0 | 0        |

| 0 | 0 | 1 | 1        |

| 0 | 1 | 0 | 0        |

| 0 | 1 | 1 | 1        |

| 1 | 0 | 0 | 1        |

| 1 | 0 | 1 | 1        |

| 1 | 1 | 0 | 0        |

| 1 | 1 | 1 | 1        |

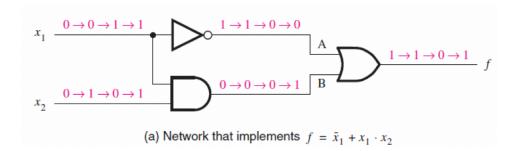

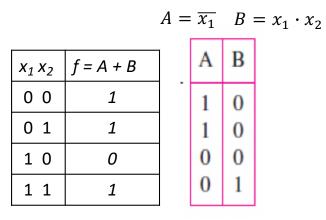

### "Composite" Logic Functions: another example

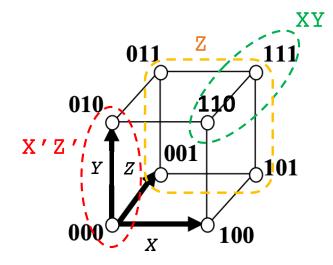

- So far we have seen 4 ways to express Logic Functions:

- Switches

• There is a fifth way called Karnaugh-maps (coming soon!)

7

1 1 0

1 1 1

1

1

# Analysis and Synthesis of Logic Functions

<u>Analysis</u> Given a logic function, determine its behavior

<u>Synthesis</u> Given a desired behavior, design the logic function that implements it

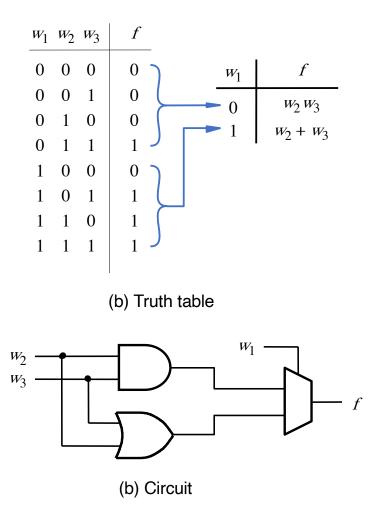

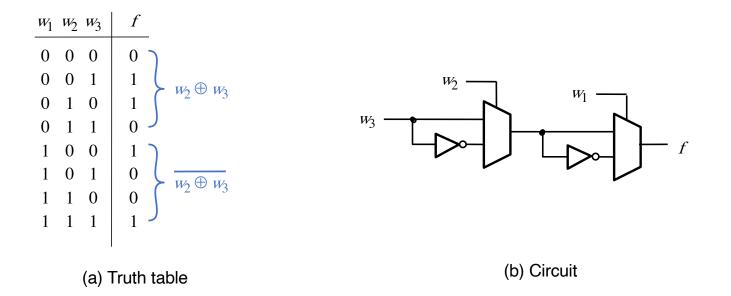

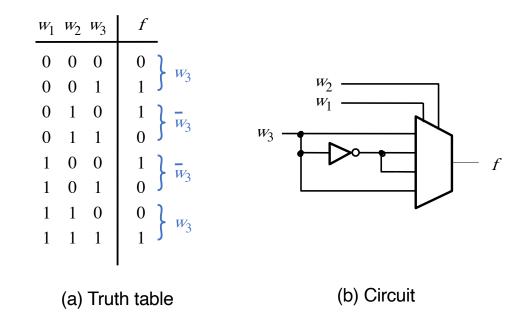

### Analysis of Logic Functions (1)

(b) Truth Table

## Analysis of Logic Functions (2)

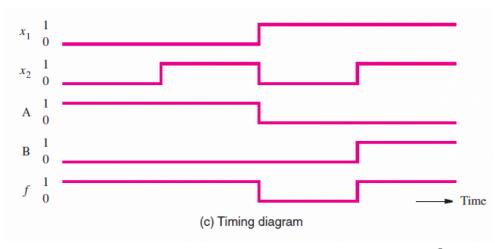

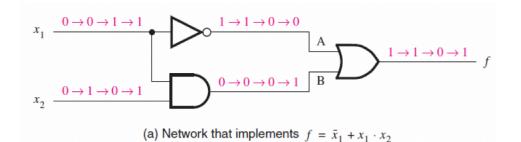

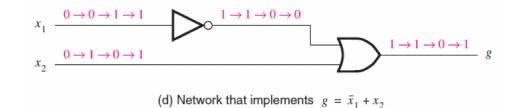

f and g behave exactly the same ! f and g are equivalent, but ... g is less "expensive" than f

It would be nice to have some systematic method to find out the less "expensive" implementation of a given logic function !

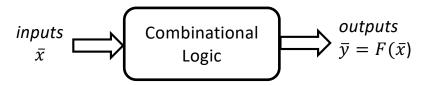

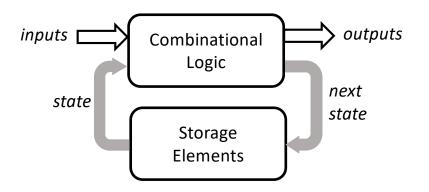

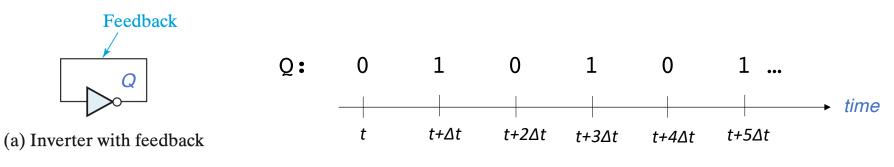

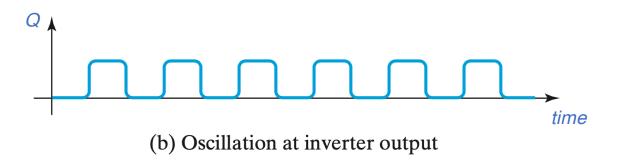

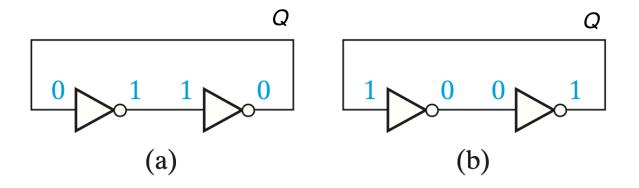

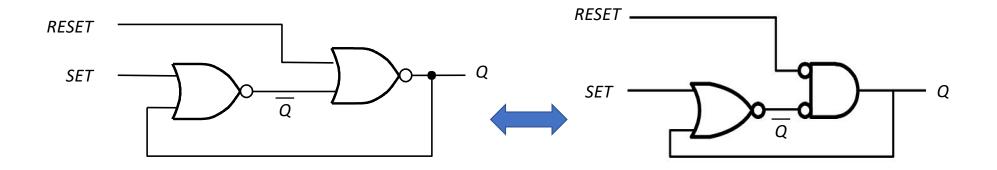

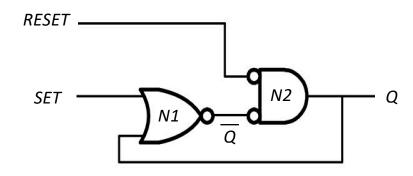

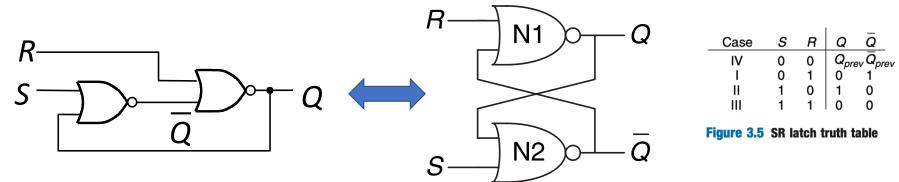

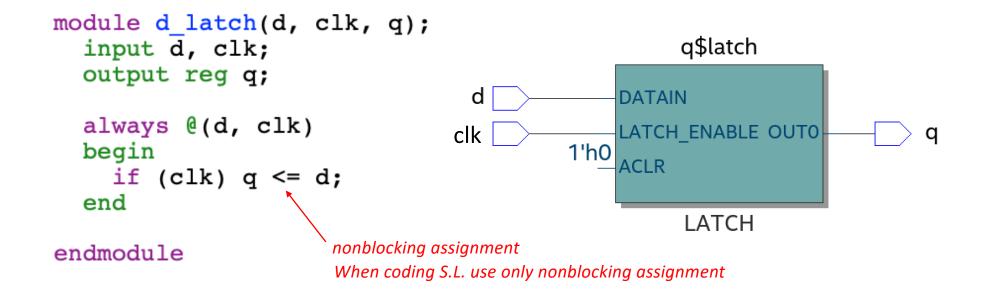

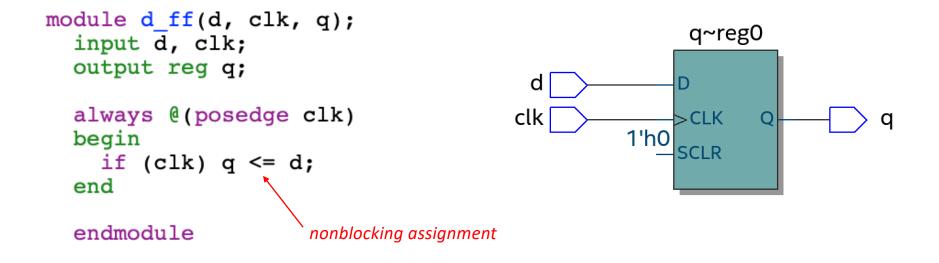

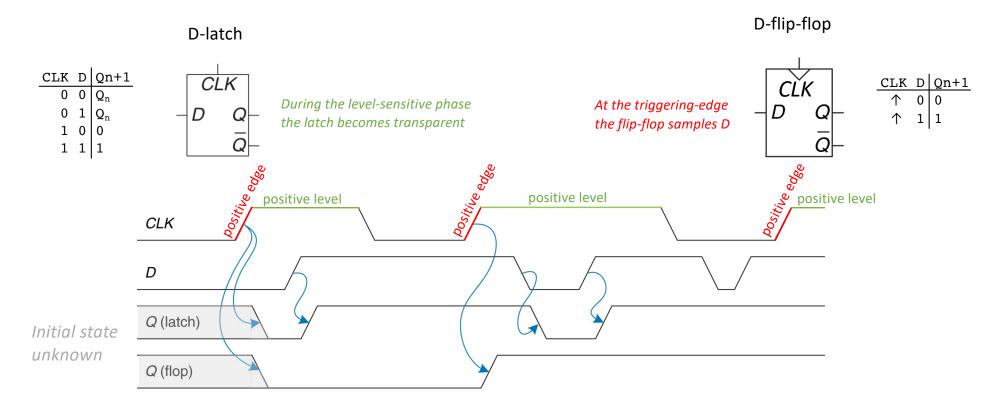

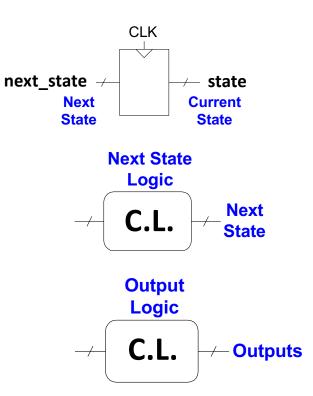

# Types of Logic Circuits

• Combinational Circuits: the output values depend only on the present value of the inputs and not on past values.

Sequential Circuits: the outputs depend on both the present and past input values

As a consequence, combinational circuits are "memory less", while sequential circuits requires storage elements (latches or flip-flops).

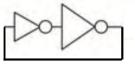

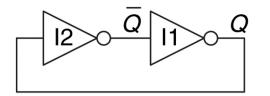

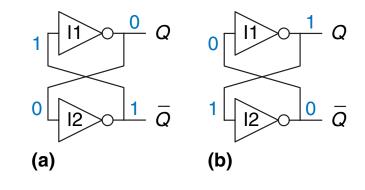

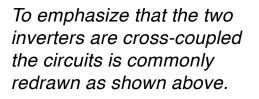

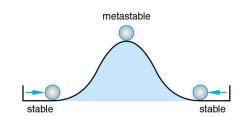

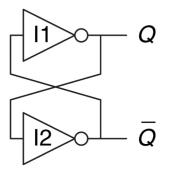

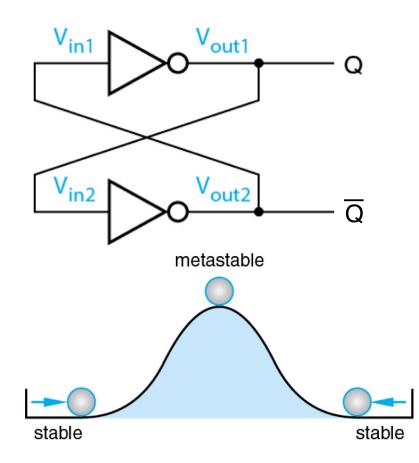

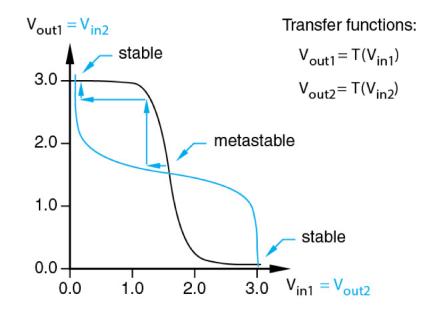

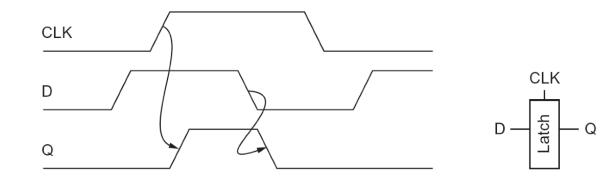

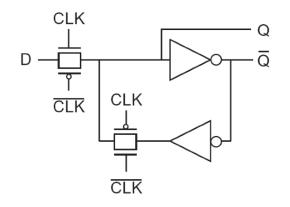

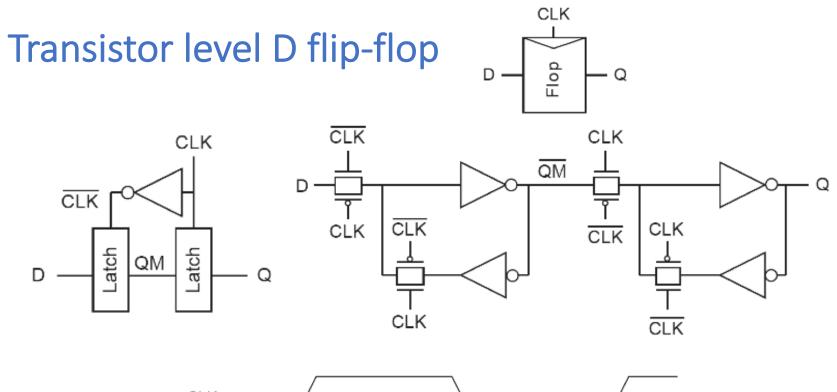

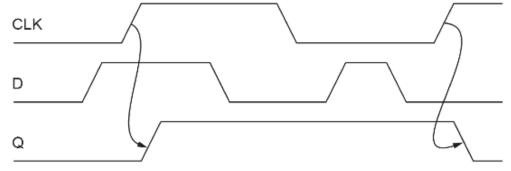

To build storage elements we need

a "feedback loop"

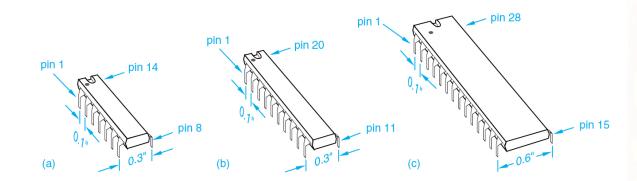

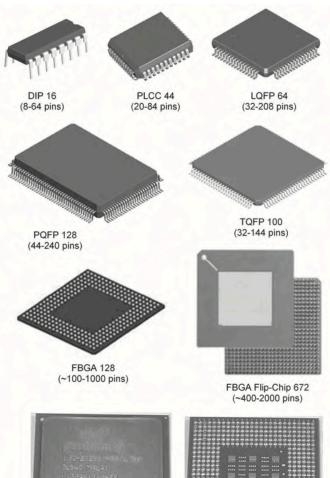

# PCBs and Integrated Circuits

| i i della |  |

|-----------------------------------------------------------------------------------------------------------------|--|

|                                                                                                                 |  |

- DIP = dual Inline Package

- SMD = Surface Mount Devices

- PLCC = Plastic Leaded Chip Carrier

- LQFP = Low-Profile Quad Flat Package

- PQFP = Plastic Quad Flat Package

- TQFP = Thin Quad Flat package

- FBGA = Fine-Pitch Ball Grid Array

- PGA = Pin Grid Array

- Standard ICs

- Programmable ICs

- Application Specific ICs

PGA2 Flip-Chip 478 Intel Pentium 4 processor (top and bottom views)

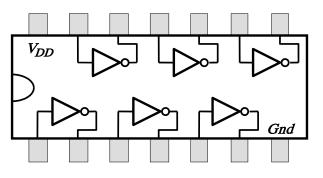

### Standard Chips (e.g. 7400-series)

(b) Structure of 7404 chip

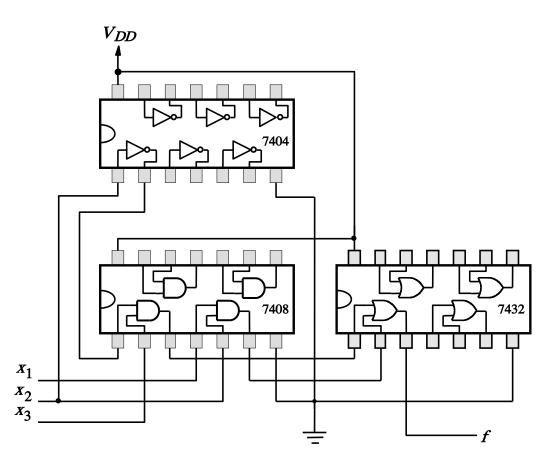

#### Implementation Example using Standard Chips

An implementation of  $f = x_1 x_2 + \overline{x}_2 x_3$

# Limitations of 7400 series standard ships:

- The function provided by each chip is fixed

- Each chip only contains a few logic gates

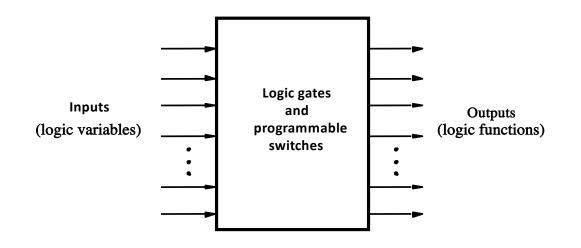

### **Programmable Logic Devices**

Programmable Logic Devices – chips that contain relatively large amounts of logic circuits with a structure that is not fixed (the structure can be customized)

Programmable logic device as a black box

### Types of Programmable Logic Devices

- There are several types of Programmable Logic Devices commercially available:

- Programmable Logic Array (PLA)

- Programmable Array Logic (PAL)

- Complex Programmable Logic Devices (CPLDs)

- Field-Programmable Gate Arrays (FPGA)

- Logic circuit elements in programmable logic devices can be customized (that is programmed) through the use of CAD tools

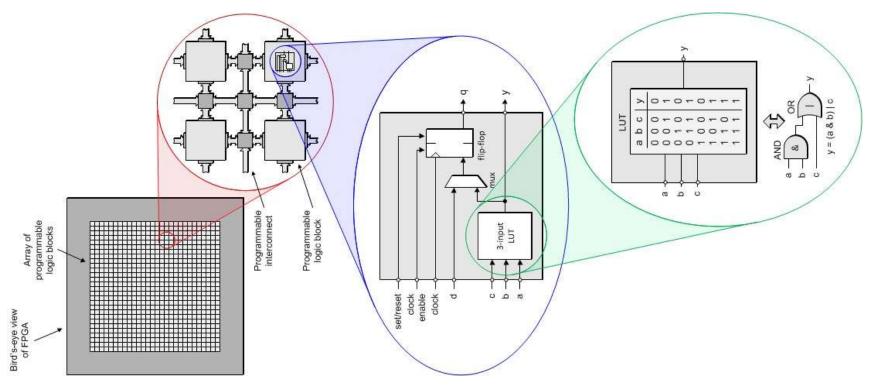

## FPGA's internal fabric

• Both the basic logic cells (LUT) an the interconnections are programmable

#### Manipulating the Basic Boolean Functions

11

0

| a b | a' b' | a' + b' |

|-----|-------|---------|

| 00  | 11    | 1       |

| 01  | 10    | 1       |

| 10  | 01    | 1       |

| 11  | 00    | 0       |

if we want we can use NAND gates for everything !

**INVERTER**

if we want we can use NOR gates for everything !

# Boolean Algebra

#### <u>Objective:</u> Systematic way of manipulating Boolean expression

• One-Variable Theorems

| $x \cdot 1 = x$  | x + 0 = x        |  |  |  |  |

|------------------|------------------|--|--|--|--|

| $x \cdot 0 = 0$  | <i>x</i> + 1 = 1 |  |  |  |  |

| $x \cdot x = x$  | x + x = x        |  |  |  |  |

| $x \cdot x' = 0$ | x + x' = 1       |  |  |  |  |

| (x')' = x        |                  |  |  |  |  |

# Boolean Algebra

#### • Two and Three-Variable Theorems

| $x + x \cdot y = x$                                           | $x \cdot (x + y) = x$                     | absorption (a.k.a. covering) |

|---------------------------------------------------------------|-------------------------------------------|------------------------------|

| $x \cdot y + x \cdot y' = x$                                  | (x+y)(x+y') = x                           | combining                    |

| $(x \cdot y)' = x' + y'$                                      | $(x+y)' = x' \cdot y'$                    | De Morgan                    |

| $x \cdot y = y \cdot x$                                       | x + y = y + x                             | commutative                  |

| $(x \cdot y) \cdot z = x \cdot (y \cdot z)$                   | (x+y) + z = x + (y+z)                     | associative                  |

| $x \cdot (y+z) = x \cdot y + x \cdot z$                       | $x + (y \cdot z) = (x + y) \cdot (x + z)$ | distributive                 |

| $x' \cdot y + x \cdot z = x' \cdot y + x \cdot z + y \cdot z$ | (x'+y)(x+z) = (x'+y)(x+z)(y+z)            | consensus (muxing)           |

#### • Duality Principle

If a Boolean function f is true then the dual function  $f_D$  is also true. The dual of a logic function f is the function  $f_D$  derived from f by swapping "+" with "•", "•" with "+", "0" with "1" and "1" with "0".

# Boolean Algebra

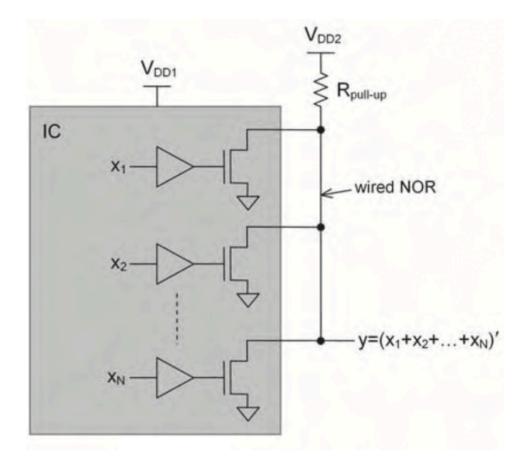

#### • N-Variable Theorems

| $(x_1 + x_2 + x_3 + \dots + x_N)' = x_1' \cdot x_2' \cdot x_3' \cdot \dots \cdot x_N'$                        | De Morgan         |

|---------------------------------------------------------------------------------------------------------------|-------------------|

| $(x_1 \cdot x_2 \cdot x_3 \cdot \dots \cdot x_N)' = x_1' + x_2' + x_3' + \dots + x_N'$                        | Theorem           |

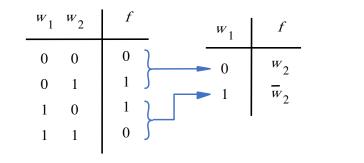

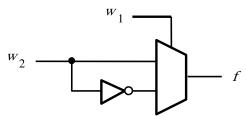

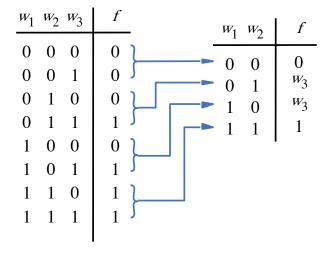

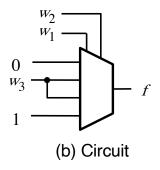

| $f(x_1, x_2, x_3, \dots, x_N) = x_1' \cdot f(0, x_2, x_3, \dots, x_N) + x_1 \cdot f(1, x_2, x_3, \dots, x_N)$ | Shannon Expansion |

| $f(x_1, x_2, x_3, \dots, x_N) = [x_1' + f(1, x_2, x_3, \dots, x_N)] \cdot [x_1 + f(0, x_2, x_3, \dots, x_N)]$ | Theorem           |

DeMorgan Theorem:

The **complement** of the **product** is the **sum** of the **complements**.

Dual:

The **complement** of the **sum** is the **product** of the **complements**.

$$\begin{array}{c} A \\ B \\ \hline \end{array} \\ \hline \\ A \\ B \\ \hline \end{array} \\ \hline \\ -Y \end{array} Y = \overline{A \cdot B} = \overline{A} + \overline{B}$$

# Next Time

- Standard Form Representations of Logic Functions:

- SOP

- POS

- min terms

- max terms

#### Consensus (a practical perspective)

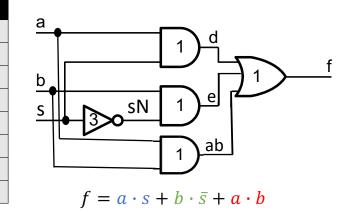

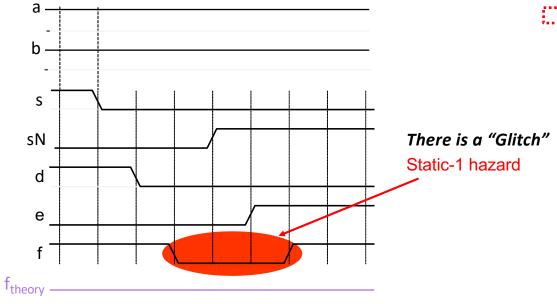

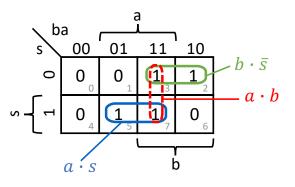

$f = a \cdot s + b \cdot \bar{s}$

#### Example. Prove Combining Theorem

$x \cdot y + x \cdot y' = x \cdot (y + y') = x \cdot 1 = x$  $(x + y) \cdot (x + y') = x \cdot x + x \cdot y + x \cdot y' + y \cdot y' = x + x \cdot (y + y') + 0 = x + x \cdot 1 + 0 = x$

Example. Prove Absorption Theorem

$$x + x \cdot y = x \cdot (y + y') + x \cdot y = x \cdot y + x \cdot y' + x \cdot y = x \cdot y + x \cdot y' = x$$

$$x \cdot (x + y) = x \cdot x + x \cdot y = x + x \cdot y = x \cdot (y + y') + x \cdot y = x \cdot y + x \cdot y' + x \cdot y = x \cdot y + x \cdot y' = x$$

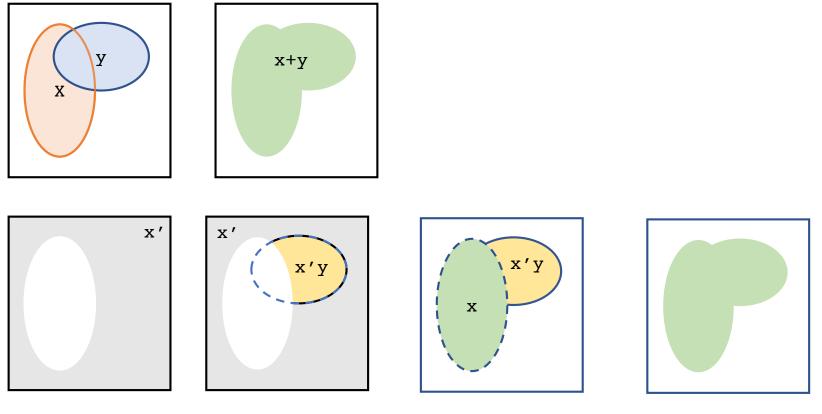

An addition tool to gain insight into a logic equation is to use <u>Venn Diagrams</u> from set theory

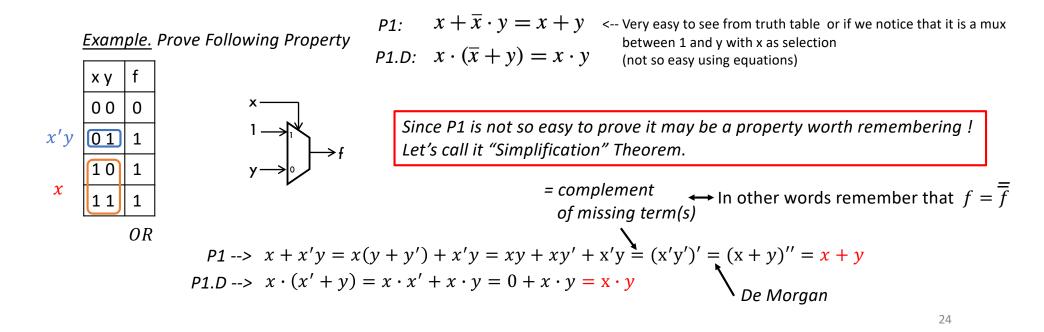

x + x'y = x + y

### How to Prove ?

- Method 1: Perfect induction

- Method 2: Use other theorems and axioms to simplify the equation

- Make one side of the equation look like the other

# What does Perfect Induction mean ?

- Despite the "fancy" name this is the most obvious solution

- Also called: **proof by exhaustion**

- Check every possible input value

- If two expressions produce the same value for every possible input combination, the expressions are equal

# Standard Forms

CPEN 230 – Introduction to Digital Logic

# Review: Boolean Algebra

#### **One-Variable Theorems**

| $x \cdot 1 = x$  | x + 0 = x        |

|------------------|------------------|

| $x \cdot 0 = 0$  | <i>x</i> + 1 = 1 |

| $x \cdot x = x$  | x + x = x        |

| $x \cdot x' = 0$ | x + x' = 1       |

| (x')' = x        |                  |

#### **Two and Three- Variable Theorems**

| $x + x \cdot y = x$                                           | $x \cdot (x + y) = x$                     | absorption (a.k.a. covering) |

|---------------------------------------------------------------|-------------------------------------------|------------------------------|

| $x \cdot y + x \cdot y' = x$                                  | (x+y)(x+y') = x                           | combining                    |

| $x + x' \cdot y = x + y$                                      | $x \cdot (x' + y) = x \cdot y$            | "simplification"             |

| $(x \cdot y)' = x' + y'$                                      | $(x+y)' = x' \cdot y'$                    | De Morgan                    |

| $x \cdot y = y \cdot x$                                       | x + y = y + x                             | commutative                  |

| $(x \cdot y) \cdot z = x \cdot (y \cdot z)$                   | (x+y) + z = x + (y+z)                     | associative                  |

| $x \cdot (y+z) = x \cdot y + x \cdot z$                       | $x + (y \cdot z) = (x + y) \cdot (x + z)$ | distributive                 |

| $x' \cdot y + x \cdot z = x' \cdot y + x \cdot z + y \cdot z$ | (x' + y)(x + z) = (x' + y)(x + z)(y + z)  | consensus (muxing)           |

### Review: Boolean Algebra

#### **Duality Principle**

If a Boolean function f is true then the dual function  $f_D$  is also true. The dual of a logic function f is the function  $f_D$  derived from f by swapping "+" with "•", "•" with "+", "0" with "1" and "1" with "0".

#### **N-Variable Theorems**

| $(x_1 + x_2 + x_3 + \dots + x_N)' = x_1' \cdot x_2' \cdot x_3' \cdot \dots \cdot x_N'$                                                                                                                                           | De Morgan<br>Theorem |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| $\frac{(x_1 \cdot x_2 \cdot x_3 \cdot \dots \cdot x_N)' = x_1' + x_2' + x_3' + \dots + x_N'}{f(x_1, x_2, x_3, \dots, x_N) = x_1' \cdot f(0, x_2, x_3, \dots, x_N) + x_1 \cdot f(1, x_2, x_3, \dots, x_N)}$                       | Shannon Expansion    |

| $\frac{f(x_1, x_2, x_3, \dots, x_N) - x_1 \cdot f(0, x_2, x_3, \dots, x_N) + x_1 \cdot f(1, x_2, x_3, \dots, x_N)}{f(x_1, x_2, x_3, \dots, x_N) = [x_1' + f(1, x_2, x_3, \dots, x_N)] \cdot [x_1 + f(0, x_2, x_3, \dots, x_N)]}$ | Theorem              |

| $[f(x_1, x_2, x_3, \dots, x_N) = [x_1 + f(1, x_2, x_3, \dots, x_N)] \cdot [x_1 + f(0, x_2, x_3, \dots, x_N)]$                                                                                                                    |                      |

# Truth Tables: min-terms and max-terms

For an N-input function a truth table has  $2^N$  rows (=  $2^N$  minterms =  $2^N$  maxterms)

| Row # | $\mathbf{x}_{2}  \mathbf{x}_{1}  \mathbf{x}_{0}$ | f | Minterm                                                          | Maxterm                                                                   |

|-------|--------------------------------------------------|---|------------------------------------------------------------------|---------------------------------------------------------------------------|

| 0     | 000                                              |   | $m_0 = \overline{x_2} \cdot \overline{x_1} \cdot \overline{x_0}$ | $M_0 = x_2 + x_1 + x_0 = \overline{m_0}$                                  |

| 1     | 001                                              |   | $m_1 = \overline{x_2} \cdot \overline{x_1} \cdot x_0$            | $M_1 = x_2 + x_1 + \overline{x_0} = \overline{m_1}$                       |

| 2     | 010                                              |   | $m_2 = \overline{x_2} \cdot x_1 \cdot \overline{x_0}$            | $M_2 = x_2 + \overline{x_1} + x_0 = \overline{m_2}$                       |

| 3     | 011                                              |   | $m_3 = \overline{x_2} \cdot x_1 \cdot x_0$                       | $M_3 = x_2 + \overline{x_1} + \overline{x_0} = \overline{m_3}$            |

| 4     | 100                                              |   | $m_4 = x_2 \cdot \overline{x_1} \cdot \overline{x_0}$            | $M_4 = \overline{x_2} + x_1 + x_0 = \overline{m_4}$                       |

| 5     | 101                                              |   | $m_5 = x_2 \cdot \overline{x_1} \cdot x_0$                       | $M_5 = \overline{x_2} + x_1 + \overline{x_0} = \overline{m_5}$            |

| 6     | 110                                              |   | $m_6 = x_2 \cdot x_1 \cdot \overline{x_0}$                       | $M_6 = \overline{x_2} + \overline{x_1} + x_0 = \overline{m_6}$            |

| 7     | 111                                              |   | $m_7 = x_2 \cdot x_1 \cdot x_0$                                  | $M_7 = \overline{x_2} + \overline{x_1} + \overline{x_0} = \overline{m_7}$ |

## Terminology

#### • Literal

Any occurrence of a variable, either in its direct form (e.g. a) or in its complemented form (e.g.  $\bar{a}$ )

#### • Product Term

A product (AND operation) of two or more literals (e.g. ab,  $a\overline{a}$ ,  $\overline{a}b$ ,  $\overline{a}bc$ , ...)

#### • Sum Term

A sum (OR operation) of two or more literals (e.g.  $\overline{a} + b$ ,  $\overline{a} + b$ , a + b + c, c + c, ...)

#### • Minterm

Given a function of N-input variables, a minterm is a product term of N literals with one literal for each input variable. (Example: given a function of three input variables  $\overline{a}bc$  is a min term, but  $\overline{a}b$  or  $\overline{a}ab$  are not)

#### • Maxterm

Given a function of N-input variables, a maxterm is a sum term of N literals with one literal for each input variable.

### Minterms and maxterms: example

| Row # | $\mathbf{x}_{2}  \mathbf{x}_{1}  \mathbf{x}_{0}$ | f | Minterm                                                          | Maxterm                                                                   |

|-------|--------------------------------------------------|---|------------------------------------------------------------------|---------------------------------------------------------------------------|

| 0     | 000                                              | 1 | $m_0 = \overline{x_2} \cdot \overline{x_1} \cdot \overline{x_0}$ | $M_0 = x_2 + x_1 + x_0 = \overline{m_0}$                                  |

| 1     | 001                                              | 1 | $m_1 = \overline{x_2} \cdot \overline{x_1} \cdot x_0$            | $M_1 = x_2 + x_1 + \overline{x_0} = \overline{m_1}$                       |

| 2     | 010                                              | 0 | $m_2 = \overline{x_2} \cdot x_1 \cdot \overline{x_0}$            | $M_2 = x_2 + \overline{x_1} + x_0 = \overline{m_2}$                       |

| 3     | 011                                              | 0 | $m_3 = \overline{x_2} \cdot x_1 \cdot x_0$                       | $M_3 = x_2 + \overline{x_1} + \overline{x_0} = \overline{m_3}$            |

| 4     | 100                                              | 0 | $m_4 = x_2 \cdot \overline{x_1} \cdot \overline{x_0}$            | $M_4 = \overline{x_2} + x_1 + x_0 = \overline{m_4}$                       |

| 5     | 101                                              | 0 | $m_5 = x_2 \cdot \overline{x_1} \cdot x_0$                       | $M_5 = \overline{x_2} + x_1 + \overline{x_0} = \overline{m_5}$            |

| 6     | 110                                              | 0 | $m_6 = x_2 \cdot x_1 \cdot \overline{x_0}$                       | $M_6 = \overline{x_2} + \overline{x_1} + x_0 = \overline{m_6}$            |

| 7     | 111                                              | 0 | $m_7 = x_2 \cdot x_1 \cdot x_0$                                  | $M_7 = \overline{x_2} + \overline{x_1} + \overline{x_0} = \overline{m_7}$ |

If a function f is specified in the form of a Truth Table, then an expression that realizes f can be obtained either by considering the rows in the table for which f=1 or by considering the rows for which f=0

$$f = m_0 + m_1 = (m_2 + m_3 + m_4 + m_5 + m_6 + m_7)' = (\overline{m_2} \cdot \overline{m_3} \cdot \overline{m_4} \cdot \overline{m_5} \cdot \overline{m_6} \cdot \overline{m_7})''$$

=  $M_2 \cdot M_3 \cdot M_4 \cdot M_5 \cdot M_6 \cdot M_7$

6

# Minterms and maxterms: example

| Row # | $\mathbf{x}_{2}  \mathbf{x}_{1}  \mathbf{x}_{0}$ | f | Minterm                                                          | Maxterm                                                                   |

|-------|--------------------------------------------------|---|------------------------------------------------------------------|---------------------------------------------------------------------------|

| 0     | 000                                              | 1 | $m_0 = \overline{x_2} \cdot \overline{x_1} \cdot \overline{x_0}$ | $M_0 = x_2 + x_1 + x_0 = \overline{m_0}$                                  |

| 1     | 001                                              | 1 | $m_1 = \overline{x_2} \cdot \overline{x_1} \cdot x_0$            | $M_1 = x_2 + x_1 + \overline{x_0} = \overline{m_1}$                       |

| 2     | 010                                              | 0 | $m_2 = \overline{x_2} \cdot x_1 \cdot \overline{x_0}$            | $M_2 = x_2 + \overline{x_1} + x_0 = \overline{m_2}$                       |

| 3     | 011                                              | 0 | $m_3 = \overline{x_2} \cdot x_1 \cdot x_0$                       | $M_3 = x_2 + \overline{x_1} + \overline{x_0} = \overline{m_3}$            |

| 4     | 100                                              | 0 | $m_4 = x_2 \cdot \overline{x_1} \cdot \overline{x_0}$            | $M_4 = \overline{x_2} + x_1 + x_0 = \overline{m_4}$                       |

| 5     | 101                                              | 0 | $m_5 = x_2 \cdot \overline{x_1} \cdot x_0$                       | $M_5 = \overline{x_2} + x_1 + \overline{x_0} = \overline{m_5}$            |

| 6     | 110                                              | 0 | $m_6 = x_2 \cdot x_1 \cdot \overline{x_0}$                       | $M_6 = \overline{x_2} + \overline{x_1} + x_0 = \overline{m_6}$            |

| 7     | 111                                              | 0 | $m_7 = x_2 \cdot x_1 \cdot x_0$                                  | $M_7 = \overline{x_2} + \overline{x_1} + \overline{x_0} = \overline{m_7}$ |

$$f = \sum m(0,1) = \prod M(2,3,4,5,6,7)$$

7

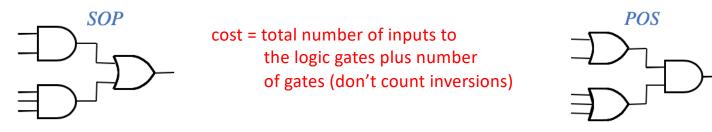

#### Sum-of-Products (SOPs) and Product-of-Sums (POSs)

Any Boolean function *f* can be expressed either as a sum of product terms (SOPs) or as a product of sum terms (POSs)

- If all the product terms in the SOP are minterms then the expression is called a normal (or canonical or standard) form SOP

- If all the sum terms in the POS are maxterms then the expression is called a normal (or canonical or standard) form POS

Example

$$f(x_2, x_2, x_1) = \sum m(0,1) = x_2' x_1' x_0' + x_2' x_1' x_0 = (x_2' x_1') (x_0' + x_0) = x_2' x_1'$$

canonical SOP form

non-canonical SOP form

### Minterms and maxterms

| Row # | $\mathbf{x}_{2}  \mathbf{x}_{1}  \mathbf{x}_{0}$ | f | Minterm                                                          | Maxterm                                                                   |

|-------|--------------------------------------------------|---|------------------------------------------------------------------|---------------------------------------------------------------------------|

| 0     | 000                                              | 0 | $m_0 = \overline{x_2} \cdot \overline{x_1} \cdot \overline{x_0}$ | $M_0 = x_2 + x_1 + x_0 = \overline{m_0}$                                  |

| 1     | 001                                              | 0 | $m_1 = \overline{x_2} \cdot \overline{x_1} \cdot x_0$            | $M_1 = x_2 + x_1 + \overline{x_0} = \overline{m_1}$                       |

| 2     | 010                                              | 0 | $m_2 = \overline{x_2} \cdot x_1 \cdot \overline{x_0}$            | $M_2 = x_2 + \overline{x_1} + x_0 = \overline{m_2}$                       |

| 3     | 011                                              | 0 | $m_3 = \overline{x_2} \cdot x_1 \cdot x_0$                       | $M_3 = x_2 + \overline{x_1} + \overline{x_0} = \overline{m_3}$            |

| 4     | 100                                              | 1 | $m_4 = x_2 \cdot \overline{x_1} \cdot \overline{x_0}$            | $M_4 = \overline{x_2} + x_1 + x_0 = \overline{m_4}$                       |

| 5     | 101                                              | 0 | $m_5 = x_2 \cdot \overline{x_1} \cdot x_0$                       | $M_5 = \overline{x_2} + x_1 + \overline{x_0} = \overline{m_5}$            |

| 6     | 110                                              | 0 | $m_6 = x_2 \cdot x_1 \cdot \overline{x_0}$                       | $M_6 = \overline{x_2} + \overline{x_1} + x_0 = \overline{m_6}$            |

| 7     | 111                                              | 0 | $m_7 = x_2 \cdot x_1 \cdot x_0$                                  | $M_7 = \overline{x_2} + \overline{x_1} + \overline{x_0} = \overline{m_7}$ |

Each minterm "touches" only one row of the truth table (e.g.  $m_4$ )

Each maxterm "touches" all but one row of the table (e.g.  $M_4 = \overline{m_4}$  so it touches:  $m_0$ ;  $m_1$ ;  $m_2$ ;  $m_3$ ;  $m_5$ ;  $m_6$  and  $m_7$ )

9

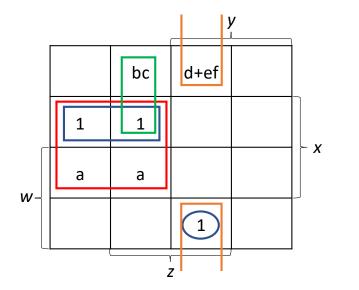

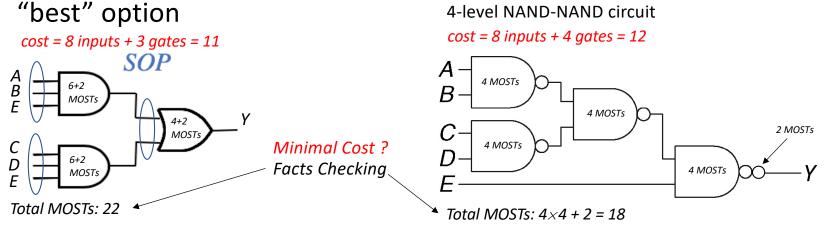

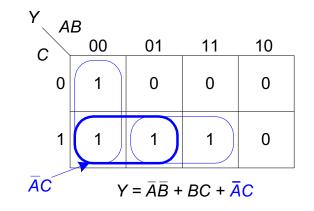

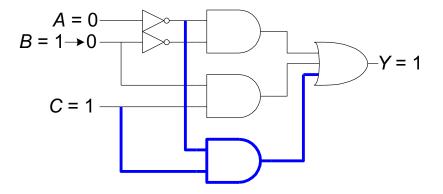

## Simplyfing an Equation

Reducing an equation to the **fewest number of implicants**, where each implicant has the **fewest literals**

#### **Recall:**

- Implicant: product of literals

ABC, AC, BC

Literal: variable or its complement

A, A', B, B', C, C'

Also called *minimizing* the equation

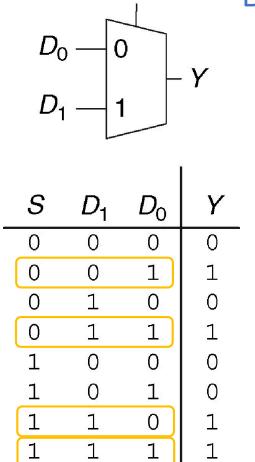

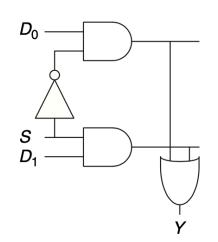

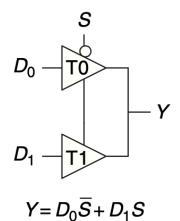

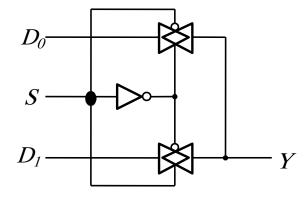

| if   | ( S | ==  | 0) |  |  |  |

|------|-----|-----|----|--|--|--|

| Y    | <=  | D0; | ;  |  |  |  |

| else |     |     |    |  |  |  |

| Y    | <=  | D1; | ;  |  |  |  |

S

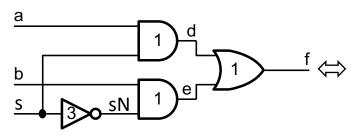

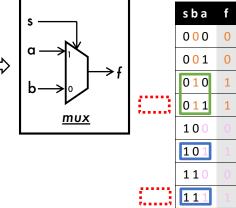

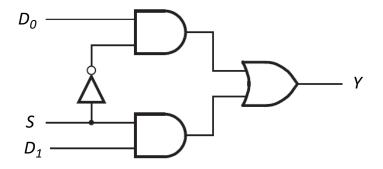

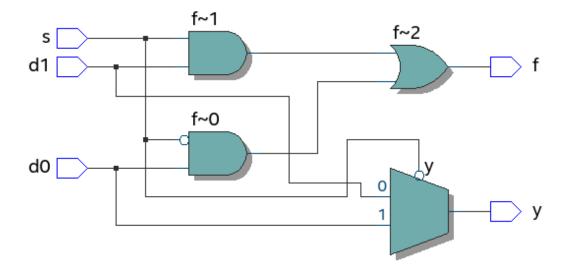

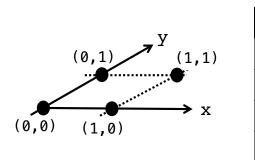

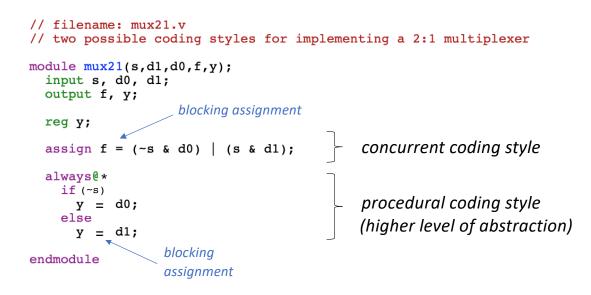

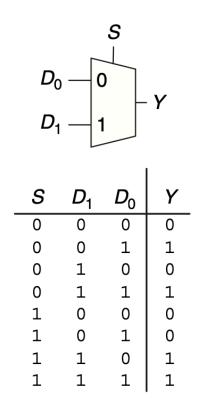

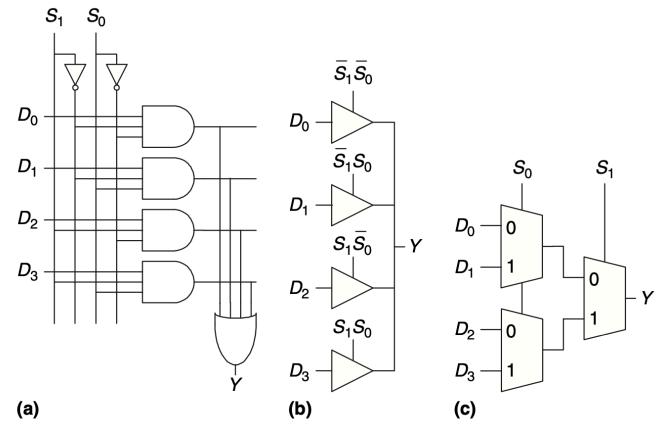

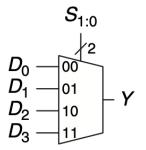

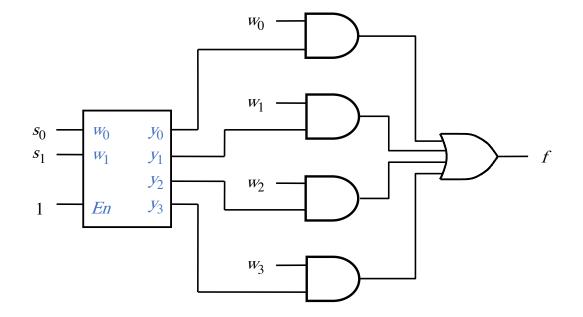

# Design Example: Multiplexer

$$Y = \sum m(1,3,6,7) =$$

$$= S \cdot D_1 \cdot D_0 + S \cdot D_1 \cdot D_0 + S \cdot D_1 \cdot D_0 + S \cdot D_1 \cdot D_0 =$$

=  $\overline{S} \cdot D_0 \cdot (\overline{D_1} + D_1) + S \cdot D_1 \cdot (\overline{D_0} + D_0) = \overline{S} \cdot D_0 + S \cdot D_1$

= 1 = 1

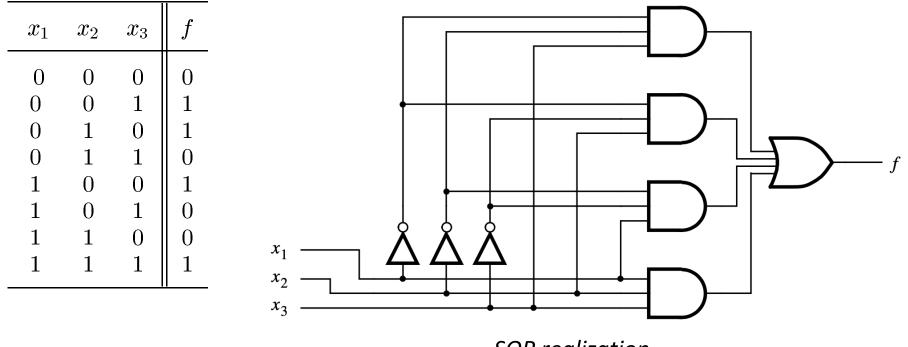

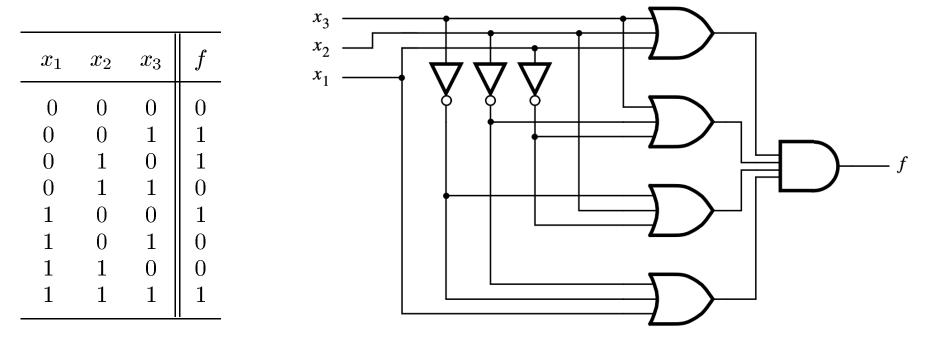

### Design Example: Three way light control

SOP realization

$f(x_1, x_2, x_3) = m_1 + m_2 + m_4 + m_7 = \overline{x_1} \cdot \overline{x_2} \cdot x_3 + \overline{x_1} \cdot x_2 \cdot \overline{x_3} + x_1 \cdot \overline{x_2} \cdot \overline{x_3} + x_1 \cdot x_2 \cdot x_3$

#### Design Example: Three way light control

POS realization

$f(x_1, x_2, x_3) = M_0 \cdot M_3 \cdot M_5 \cdot M_6 = (x_1 + x_2 + x_3) \cdot (x_1 + \overline{x_2} + \overline{x_3}) \cdot (\overline{x_1} + x_2 + \overline{x_3}) \cdot (\overline{x_1} + \overline{x_2} + x_3)$

13

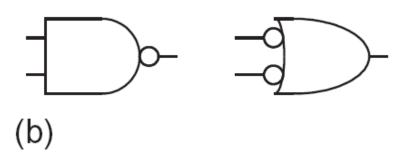

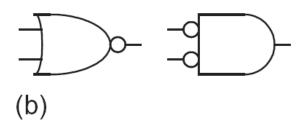

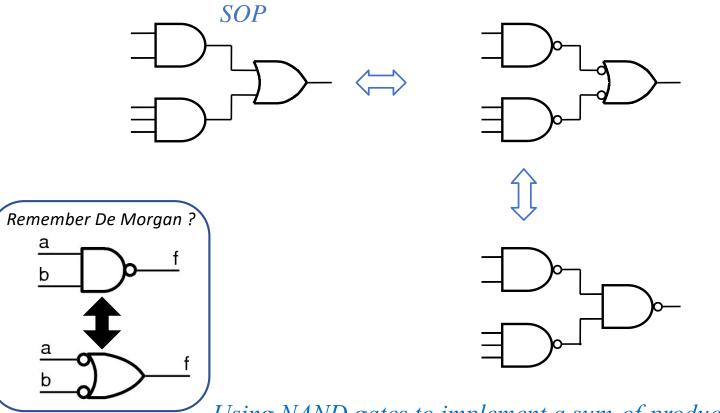

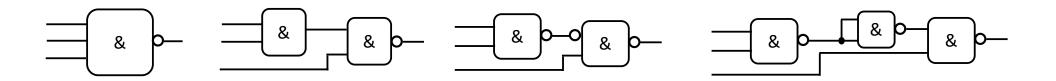

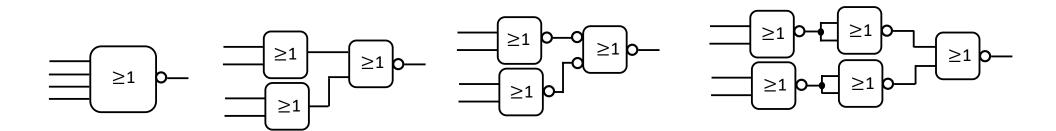

## NAND-NAND circuits (pushing bubbles)

Using NAND gates to implement a sum-of-products.

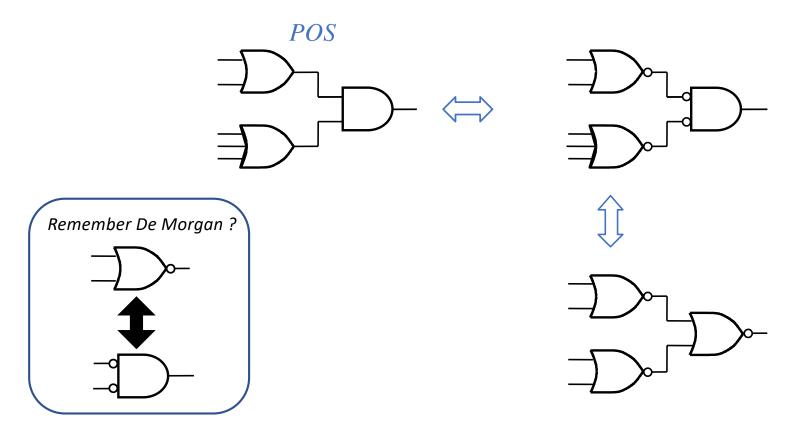

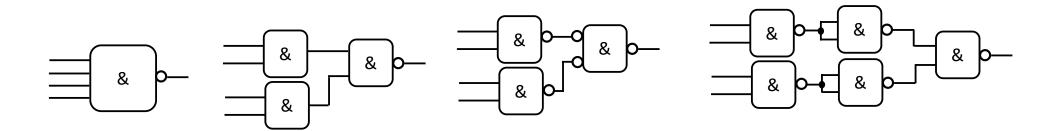

## NOR-NOR circuits (pushing bubbles)

Using NOR gates to implement a product-of sums.

## **Bubble Pushing**

#### • Backward:

- Body gets "squished" (changes shape)

- Adds bubbles to inputs

#### • Forward:

- Body gets "squished" (changes shape)

- Adds bubble to output

### NAND-NAND vs. NOR-NOR

The propagation delay through a logic gate is proportional to the RC of the switches involved in delivering the desired logic level (either V<sub>DD</sub> or GND) to the output. The switches (MOS transistors) are not ideal: they have R and C associated to them (the PMOS transistors have more R than the NMOS transistors)

#### <u>2-input CMOS NOR gate</u>

17

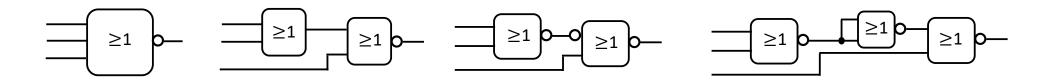

Building multiple-input NAND gates using 2-input NAND gates (pushing bubbles)

Building multiple-input NOR gates using 2-input NOR gates (pushing bubbles)

## Next Time

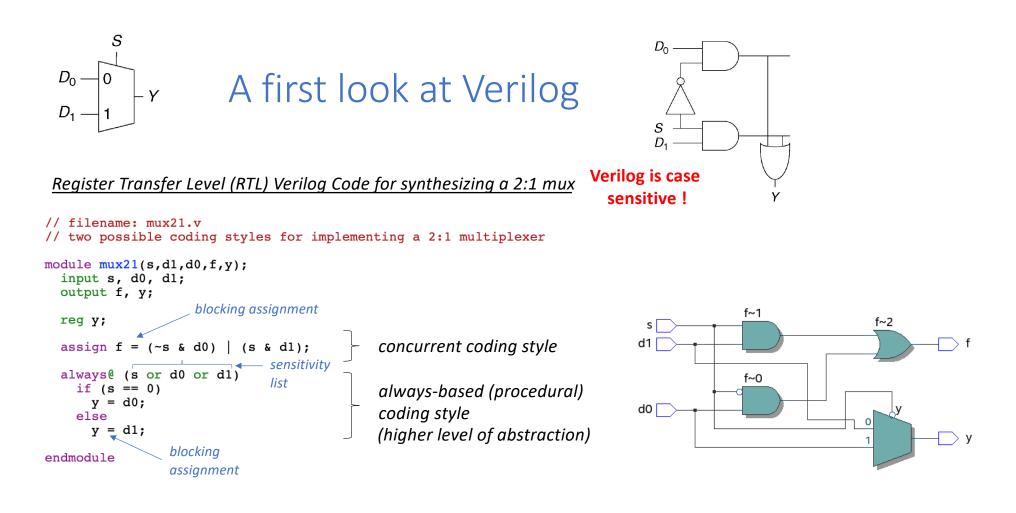

- A first look at Verilog

- K-maps

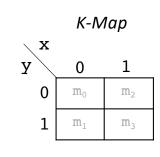

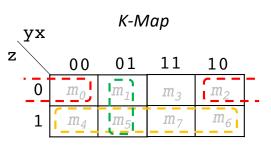

- Minimization of Boolean Equations using K-maps

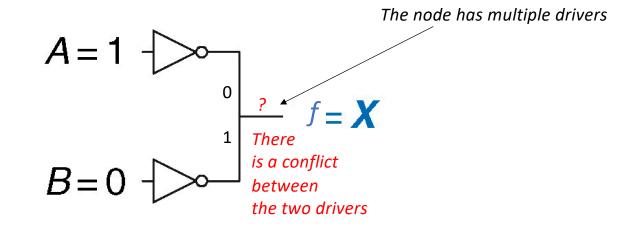

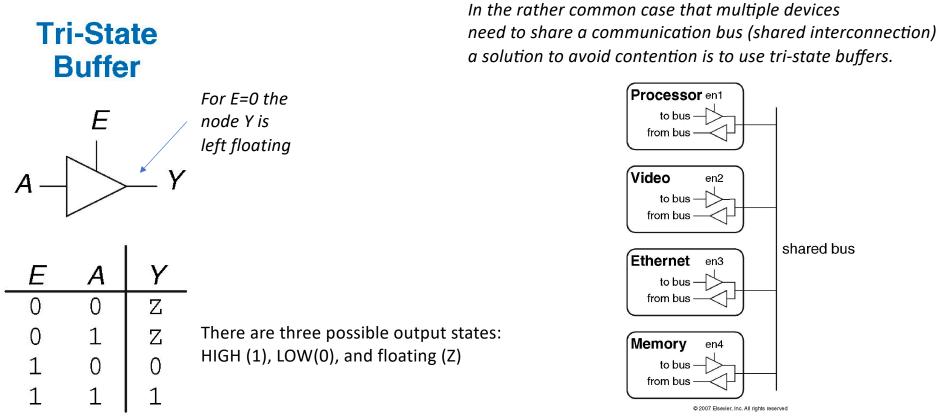

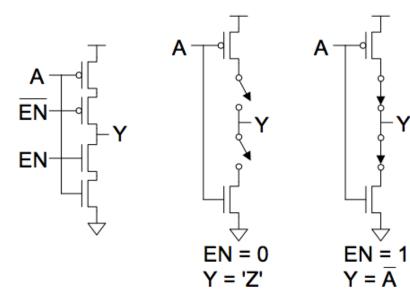

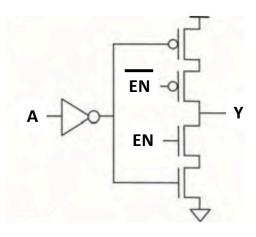

- Multiple Drivers (contention Value: X)

- Tri-state Buffer (high impedance state: Z)

# K-maps and minimization

CPEN 230 – Introduction to Digital Logic

### Review: minterms, maxterms, SOP form and POS form

| Row # | $\mathbf{x}_{2}  \mathbf{x}_{1}  \mathbf{x}_{0}$ | f | Minterm                                                          | Maxterm                                                                   |

|-------|--------------------------------------------------|---|------------------------------------------------------------------|---------------------------------------------------------------------------|

| 0     | 000                                              | 1 | $m_0 = \overline{x_2} \cdot \overline{x_1} \cdot \overline{x_0}$ | $M_0 = x_2 + x_1 + x_0 = \overline{m_0}$                                  |

| 1     | 001                                              | 1 | $m_1 = \overline{x_2} \cdot \overline{x_1} \cdot x_0$            | $M_1 = x_2 + x_1 + \overline{x_0} = \overline{m_1}$                       |

| 2     | 010                                              | 0 | $m_2 = \overline{x_2} \cdot x_1 \cdot \overline{x_0}$            | $M_2 = x_2 + \overline{x_1} + x_0 = \overline{m_2}$                       |

| 3     | 011                                              | 0 | $m_3 = \overline{x_2} \cdot x_1 \cdot x_0$                       | $M_3 = x_2 + \overline{x_1} + \overline{x_0} = \overline{m_3}$            |

| 4     | 100                                              | 0 | $m_4 = x_2 \cdot \overline{x_1} \cdot \overline{x_0}$            | $M_4 = \overline{x_2} + x_1 + x_0 = \overline{m_4}$                       |

| 5     | 101                                              | 0 | $m_5 = x_2 \cdot \overline{x_1} \cdot x_0$                       | $M_5 = \overline{x_2} + x_1 + \overline{x_0} = \overline{m_5}$            |

| 6     | 110                                              | 0 | $m_6 = x_2 \cdot x_1 \cdot \overline{x_0}$                       | $M_6 = \overline{x_2} + \overline{x_1} + x_0 = \overline{m_6}$            |

| 7     | 111                                              | 0 | $m_7 = x_2 \cdot x_1 \cdot x_0$                                  | $M_7 = \overline{x_2} + \overline{x_1} + \overline{x_0} = \overline{m_7}$ |

$$f = \sum m(0,1) = \prod M(2,3,4,5,6,7)$$

2

```

// set time format to be ns

// filename: mux21 tb.v

initial $timeformat(-9, 1, "ns", 10);

// verify the functionality of mux21.v

/*

* $timeformat(unit, precision, "unit", minwidth);

// set time tick units and precision to ns

* unit is the base that time is to be displayed, from 0 to -15 (s to fs)

'timescale 1ns / 1ns

* precision is the number of decimal points to display

* "unit" is a string appended to the time, such as " ns".

module mux21_tb;

* minwidth is the minimum number of characters that will be displayed.

*/

// UUT inputs

// output the simulation in graphical format

reg s;

initial begin

reg d0;

$dumpfile("mux21.vcd");

reg d1;

$dumpvars(0, mux21 tb);

// UUT outputs

wire f, y;

end

// generate test patterns

// variables

initial begin

integer i;

i = 0;

repeat (8) begin

// instantiate the unit under test (UUT)

\{s, d1, d0\} = i;

mux21 uut(

#1;

.<mark>s</mark>(s),

i = i+1;

.d1(d1),

end

.d0(d0),

$finish;

.<u>f</u>(f),

end

•<mark>y</mark>(y)

);

// output the simulation in textual format

initial begin

// initialize inputs

$display("time s d0 d1 f y");

// output table: header

initial begin

$display("------"); // output table: header

$monitor("%4d %1d %1d %1d %1d %1d", // output table: signal formatting

s = 0;

d1 = 0;

// output table: signals

$time, s, d0, d1, f, y);

d0 = 0;

end

end

endmodule

```

4

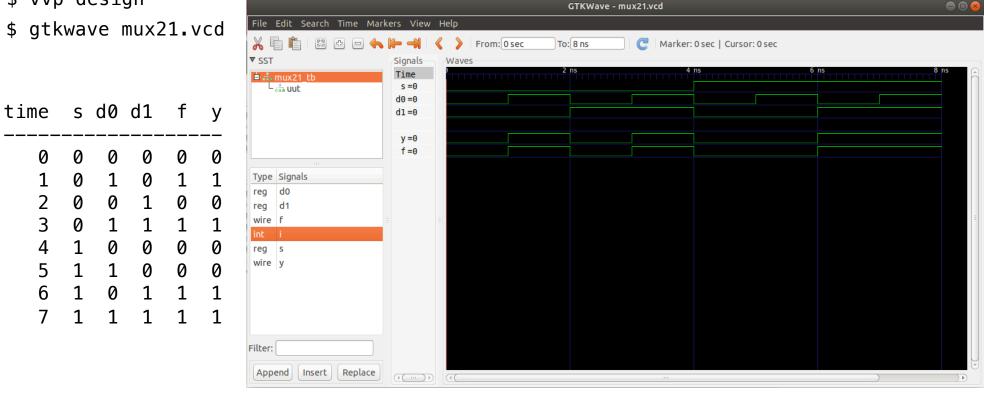

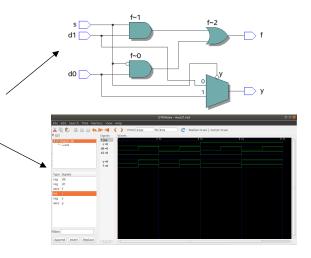

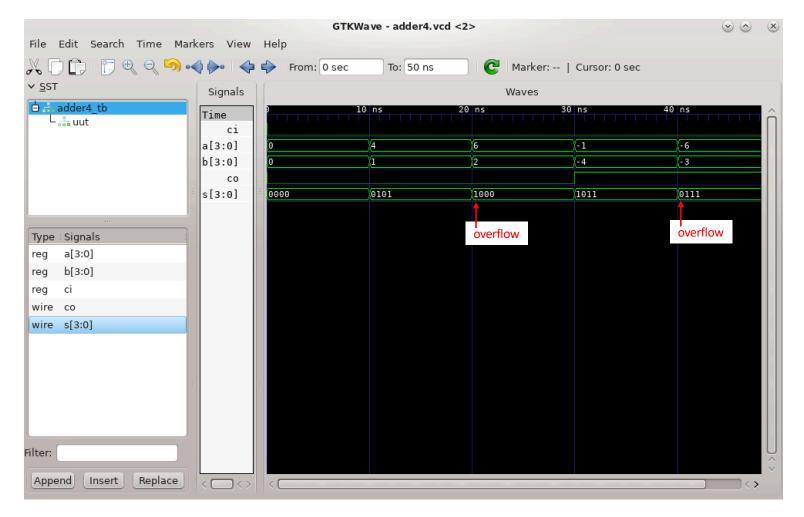

### A first look at Verilog (iverilog and GTKwave)

- iverilog -o design mux21.v mux21\_tb.v \$

- \$ vvp design

- \$ gtkwave mux21.vcd

#### A first look at Verilog (Modelsim)

VSIM 2> Now: 8 ns Delta: 0

| runmux.scr                           | ModelSim - INTEL FPGA STARTER EDITION 10.5b 💿 🗐 😣                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |          |  |  |  |  |  |

|--------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|--|--|--|--|--|

| 1 unmux : 3C1                        | <u>Eile E</u> dit <u>V</u> iew <u>C</u> ompile <u>S</u> imulate A <u>d</u> d <b>St<u>r</u>ucture</b> T <u>o</u> ols Layo <u>u</u> t Boo <u>k</u> marks <u>W</u> indow <u>H</u> elp                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |          |  |  |  |  |  |

| #!/bin/bash                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |          |  |  |  |  |  |

| vlib work                            | Layout Simulate 🗸 ColumnLayout AllColumns 🗸 🥵 🖧 🖓 🖓 🖓 🥵 🥵 🖓 🖓 🖓 👘 🖓 👘 🖓 👘 🖓 👘 🖓                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |          |  |  |  |  |  |

| vlog –work work "./mux21.v"          | _ 같 날 관 관 권 코 코 글   3+ + - K + 중+   Search: 🔽 🖉 總裁 🐡   영 영 역 은 삶 형   🏾 💵   ■ 『 」 」   🗶 米 因 🐐                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |          |  |  |  |  |  |

| vlog -work work "./mux21_tb.v"       | 👰 sim - Default :                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |          |  |  |  |  |  |

| vsim work.mux21_tb -do simmux.do     | ▼ Instance       Design unit Design unit Top Category       ▼ N ™ ■ Now ♥ ↓ ↓       Msgs         □ □ □ □ □ □ □ □ □ □ □ □ □ □ □ □ □ □ □                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |          |  |  |  |  |  |

|                                      | Ultrating and the second secon |          |  |  |  |  |  |

|                                      | K #vsim_capacity # Capacity Statistics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |          |  |  |  |  |  |

| simmux.do                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |          |  |  |  |  |  |

| restart –f                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |          |  |  |  |  |  |

|                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |          |  |  |  |  |  |

| add wave sim:/mux21_tb/*<br>run –all |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |          |  |  |  |  |  |

|                                      | Active) :::::: ± ♂ ×     Name                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |          |  |  |  |  |  |

| # quit                               | #INITIAL#52                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |          |  |  |  |  |  |

|                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |          |  |  |  |  |  |

|                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |          |  |  |  |  |  |

| \$ ./runmux.scr                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |          |  |  |  |  |  |

|                                      | At a second sec  | <u> </u> |  |  |  |  |  |

|                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |          |  |  |  |  |  |

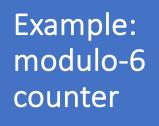

|                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | + # ×    |  |  |  |  |  |