# Capacitance of Forward Biased Diode

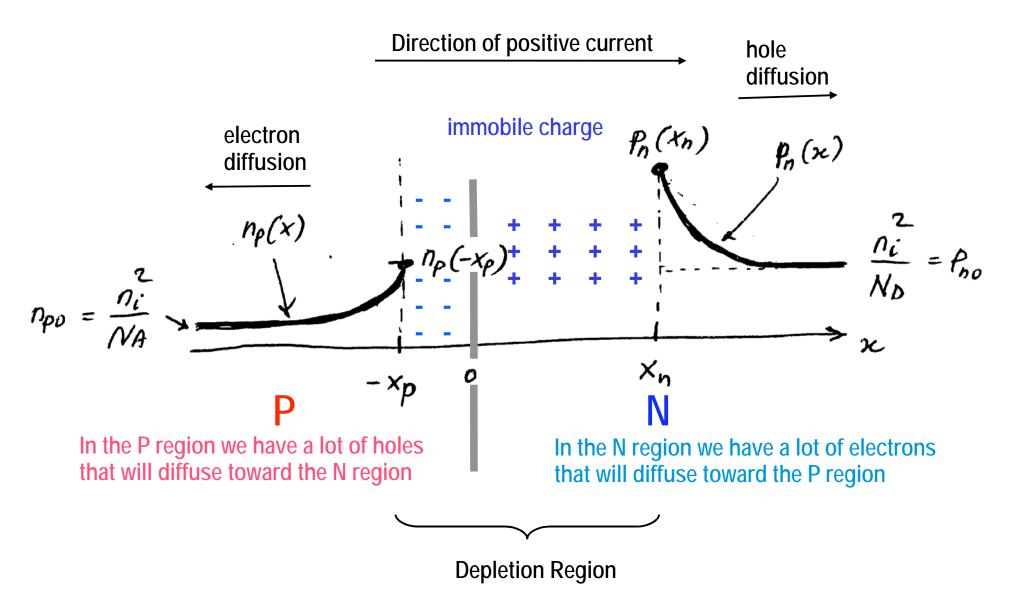

- When a diode changes from reverse biased (with little current through it) to forward biased (with significant current across it) the charge being stored near and across the junction changes

- Part of the change in charges is due to the change in the width of the depletion region and therefore the amount of immobile charge stored in it  $(\rightarrow C_j)$

- An additional change in the charge storage is necessary to account for the excess of minority carriers close to the depletion region edges required for the diffusion current to exists. This component is modeled by another capacitance, called the diffusion capacitance ( $\rightarrow C_d$ )

- As a diode is turned off (changes from forward biased to reverse biased) for a short period of time a current will flow in the negative direction until the minority charge is removed

## **Charge of Forward Biased Diode**

### **Total Capacitance of Forward Biased Diode**

• It is the sum of the diffusion capacitance Cd and the depletion capacitance Cj

$$C_{total} = C_d + C_j$$

• For a forward biased diode the junction capacitance is roughly approximated by:

$$C_{j} \approx 2 \cdot C_{j0}$$

$$(C_{j} = 2 \cdot C_{j0} \quad for V_{D} = 0.75 \cdot \phi_{0})$$

• The approximation is not critical since the diffusion capacitance is typically much larger than than the depletion capacitance

$$C_d \gg C_j$$

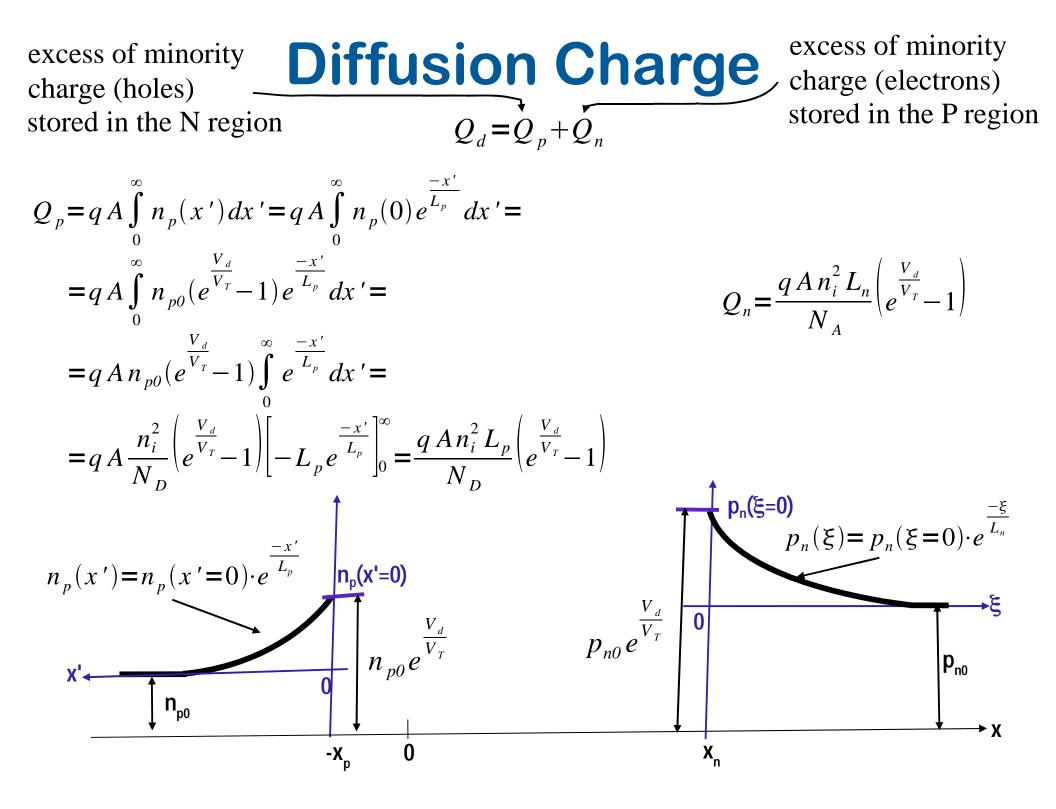

# **Diffusion Capacitance**

• To find the diffusion capacitance we first find the minority charge "close" the depletion edges Qd and then differentiate it with respect to the voltage applied Vd.

Small signal diffusion capacitance  $C_d = \left[ \frac{dQ_d}{dV_d} \right]_{V_D} = \tau_T \frac{I_d(@V_D)}{V_T}$

The diffusion capacitance of a forward biased diode is proportional to the diode current

#### **Diffusion Charge**

• The excess hole charge stored in the N region is given by:

$$Q_{p} = A q [p_{n}(x_{n}) - p_{n0}] L_{p} = P_{n0}(e^{V_{d}/V_{T}} - 1)$$

$$Q_{p} = A q [p_{n}(x_{n}) - p_{n0}] L_{p} = A q L_{p} p_{n0}(e^{V_{d}/V_{T}} - 1) = A q L_{p} p_{n0}(e^{V_{d}/V_{T}} - 1) = A J_{p} \frac{L_{p}^{2}}{D_{p}} = I_{p} \frac{L_{p}^{2}}{D_{p}} = I_{p} \tau_{p}$$

$$P_{n0}(e^{V_{d}/V_{T}} - 1) = J_{p} \frac{L_{p}}{q D_{p}}$$

$$L_{p} = \sqrt{D_{p} \tau_{p}}$$

• Similarly, the excess electron charge stored in the P region is:

$$Q_n = I_n \tau_n$$

# **Total Diffusion Charge**

• Thus, the total excess minority carrier charge is:

$$Q_d = Q_p + Q_n = I_p \tau_p + I_n \tau_n$$

• Since the diode current is  $I_d = I_p + I_n$  it is more convenient to express the excess charge as:

$Q_d = \tau_T \cdot I_d$  (where  $\tau_T$  is called **mean transit time**)

#### **Diffusion Capacitance**

$$C_{d} = \left[\frac{dQ_{d}}{dV_{d}}\right]_{V_{D}} = \left[\frac{d\left(\tau_{T}I_{d}\right)}{dV_{d}}\right]_{V_{D}} = \tau_{T}\left[\frac{dI_{d}}{dV_{d}}\right]_{V_{D}} = \frac{\tau_{T}}{r_{d}}$$

$$\frac{1}{r_{d}} = \left[\frac{dI_{d}}{dV_{d}}\right]_{V_{D}} = \left[\frac{d\left(I_{s} \cdot \left(e^{\frac{V_{d}}{V_{T}}} - 1\right)\right)}{dV_{d}}\right]_{V_{D}} = \left[\frac{I_{s}e^{\frac{V_{d}}{V_{T}}}}{V_{T}}\right]_{V_{D}} = \left[\frac{I_{d}+I_{s}}{V_{T}}\right]_{V_{D}} \approx \left[\frac{I_{d}}{V_{T}}\right]_{V_{D}}$$

$$C_{d} \approx \tau_{T}\left[\frac{I_{d}}{V_{T}}\right]_{V_{D}}$$

#### **Transition Time**

• The general expression for  $\tau_{T}$  is quite cumbersome:

$$\tau_T = C_d \cdot r_d$$

$$where \quad \frac{1}{r_d} \equiv \left[ \begin{array}{c} \frac{dI_d}{dV_d} \end{array} \right]_{V_D} \qquad with \qquad I_d = \left( \frac{qAD_n}{L_n} \frac{n_i^2}{N_A} + \frac{qAD_p}{L_p} \frac{n_i^2}{N_D} \right) \left( e^{\frac{V_d}{V_T}} - 1 \right)$$

$$C_d = \left[ \begin{array}{c} \frac{dQ_d}{dV_d} \end{array} \right]_{V_D} \qquad with \qquad Q_d = \left( \frac{qAn_i^2L_p}{N_D} + \frac{qAn_i^2L_n}{N_A} \right) \left( e^{\frac{V_d}{V_T}} - 1 \right)$$

#### **Transition Time**

In practice, since usually diodes are single sided (i.e. one side will be much more heavily doped than the other side) the minority charge storage in the heavily doped side can be ignored

$$Q_{p} = \frac{q A n_{i}^{2} L_{p}}{N_{D}} \left( e^{\frac{V_{d}}{V_{T}}} - 1 \right) \qquad \qquad Q_{n} = \frac{q A n_{i}^{2} L_{n}}{N_{A}} \left( e^{\frac{V_{d}}{V_{T}}} - 1 \right)$$

• Assuming the P side is more heavily doped than the N side:

# **Single Sided Diodes**

- One side of the diode is more heavily doped than the other

- Many of the junctions encountered in integrated circuits are onesided junctions with the lightly doped side being the substrate or the well.

- Foe single sided diodes the depletion region will extend mostly on the lightly doped side.

- The depletion capacitance is almost independent of the doping concentration on the heavily doped side

# **Single Sided Diodes**

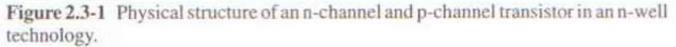

- The PN junctions inside CMOS ICs are single-sided

- NMOS transistors have parasitic diodes with the N side more heavily doped than the P side:  $N_D \gg N_A$

- PMOS transistors have parasitic diodes with the P side more heavily doped than the N side:  $N_A \gg N_D$

- NOTE: in general within an MOS transistor, it is undesirable to have a forward biased junction, it usually means there is a problem.

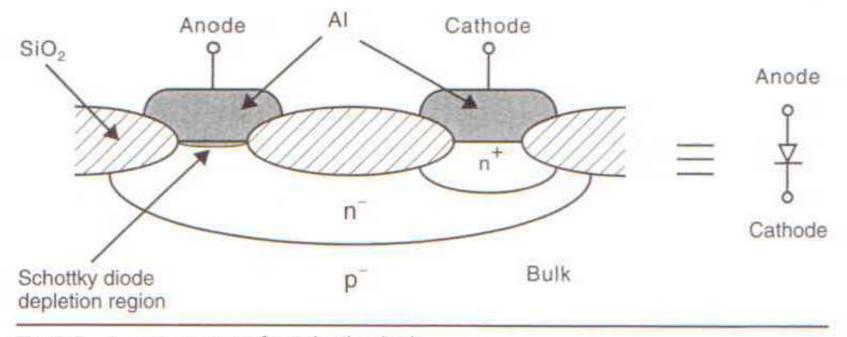

# **Schottky Diodes**

- A different type of diode, can be realized by contacting a metal to a lightly doped semiconductor region.

- The use of a lightly doped semiconductor, causes a depletion region to form at the interface between the aluminum anode and the n+ silicon region

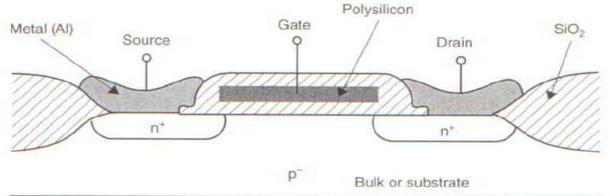

Fig. 1.5 A cross section of a Schottky diode.

# **Schottky Diodes**

- The voltage drop of a forward biased Schottky diode is smaller. The value depends on the metal used. For aluminum is approx 0.5 V

- When the diode is forward biased there is no minority charge storage in the lightly doped n+ region. Thus Cd = 0

- The absence of diffusion capacitance makes the diode much faster.

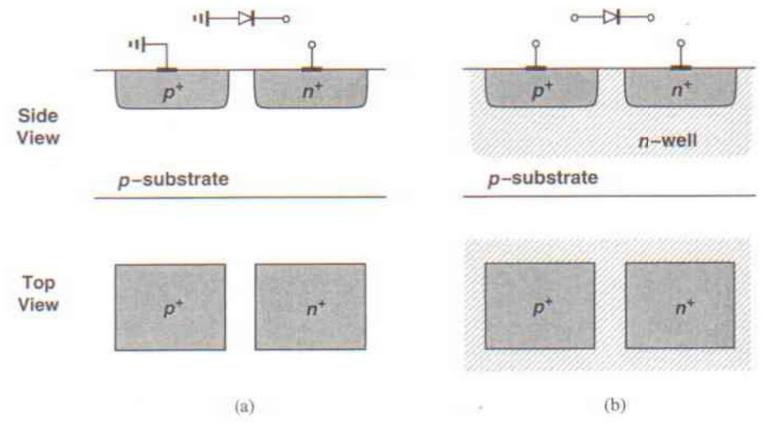

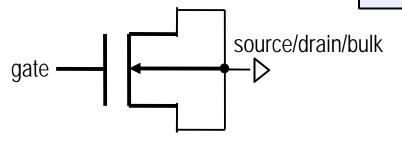

#### **Diodes realized in CMOS technology**

Figure 14.54 Diodes realized in CMOS technology.

#### NOTE: For the case of Fig 14.54(a) the anode is inevitably grounded

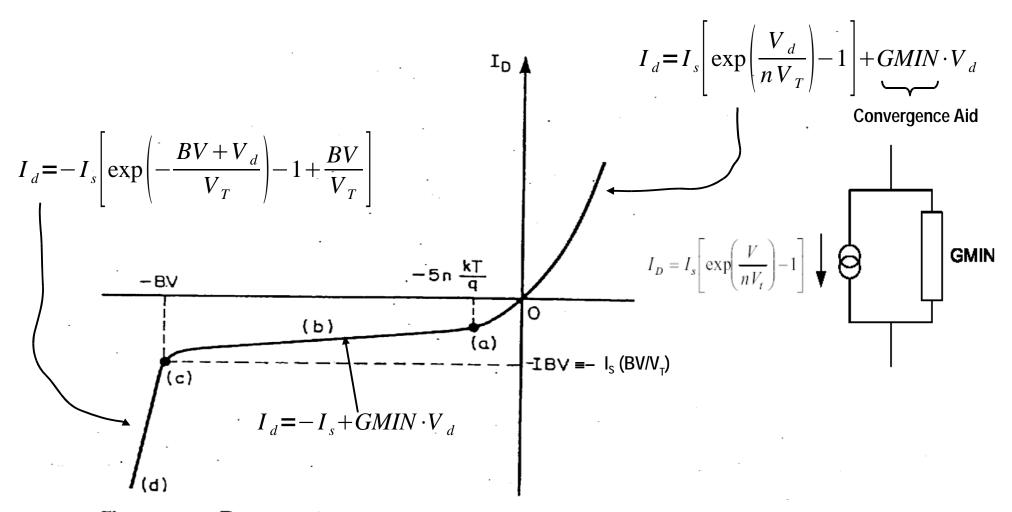

### **Diode SPICE model**

| Parameter       | SPICE       | Description                                                 |

|-----------------|-------------|-------------------------------------------------------------|

|                 |             |                                                             |

| I <sub>S</sub>  | IS          | Saturation Current                                          |

| R <sub>s</sub>  | RS          | Ohmic Series Resistance of the p-n regions and the contacts |

| n               | Ν           | Emission Coefficient                                        |

| $\phi_0$        | VJ, PB, PHI | Built-in Voltage                                            |

| C <sub>j0</sub> | CJ0, CJ     | Zero Bias Junction Capacitance                              |

| M <sub>j</sub>  | MJ, M       | Grading Coefficient                                         |

| $\tau_{T}$      | TT          | Transit Time                                                |

| V <sub>K</sub>  | BV          | Reverse Breakdown Knee Voltage                              |

| I <sub>K</sub>  | IBV         | Reverse Breakdown Knee Current                              |

#### **Diode SPICE Modeling**

Figure 1-15 Reverse characteristic of the real diode.

From: P. ANTOGNETTI, G. MASSOBRIO Semiconductor device modeling with SPICE 18 McGraw-Hill, New York, 1988

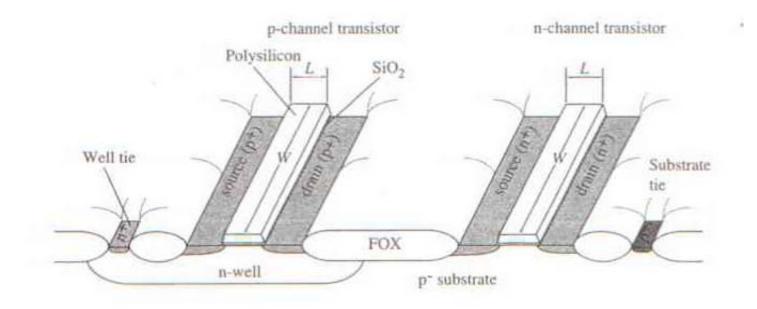

#### **MOS physical structure**

Fig. 1.6 A cross section of a typical n-channel transistor.

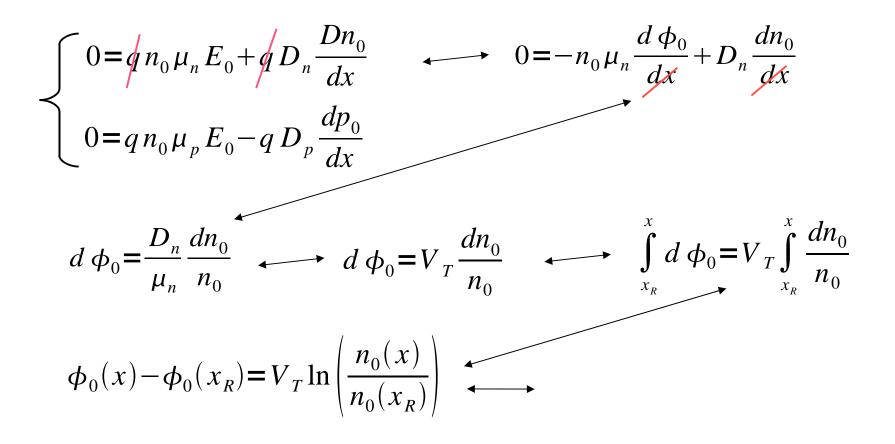

# **Thermal Equilibrium**

- Absence of any stimulus to the device

- The populations of electrons and holes are each in equilibrium and, therefore must have zero current densities

### **Thermal Equilibrium**

$\phi_0(x_R) = 0$  when  $n_0(x_R) = n_i$

$$\longleftrightarrow \phi_0(x) - \phi_0(x_R) = V_T \ln\left(\frac{n_0(x)}{n_0(x_R)}\right)$$

By convention the reference for the potential is chosen to be the point where the carrier concentration is the intrinsic concentration

$$\phi_0(x) = V_T \ln\left(\frac{n_0(x)}{n_i}\right) \qquad \longleftarrow \qquad n_0(x) = n_i e^{\frac{\phi_0(x)}{V_T}}$$

NOTE: for N type silicon since  $n_0 > n_i$  the electrostatic potential at equilibrium is positive

# **Thermal Equilibrium**

A similar derivation for the hole concentration leads to the following result:

$$\phi_0(x) = -V_T \ln\left(\frac{p_0(x)}{n_i}\right) \qquad \longleftarrow \qquad p_0(x) = n_i e^{\frac{-\phi_0(x)}{V_T}}$$

NOTE: for P type silicon since  $p_0 > n_i$  the electrostatic potential at equilibrium is negative

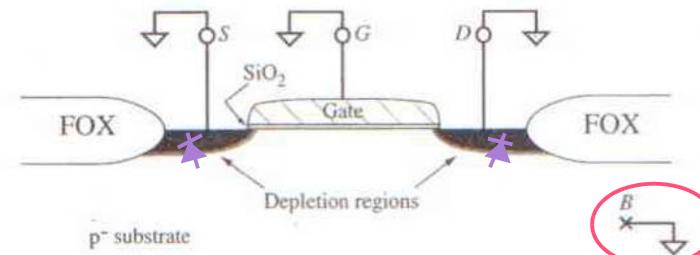

# MOS Capacitor in Thermal Equilibrium

At equilibrium the psubstrate and the n+ source and drain form a pn junction. Therefore a depletion region exists between the n+ source and drain and the p- substrate

Figure 2.3-2 Cross section of an n-channel transistor with all terminals grounded.

Since source and drain are separated by back-toback junctions, the resistance between the source and the drain is very high (> 10<sup>12</sup> ohm)

Figure. Using the MOSFET as a capacitor

The gate and the substrate of the MOS transistor form a parallel plate capacitor with the SiO<sub>2</sub> as dielectric

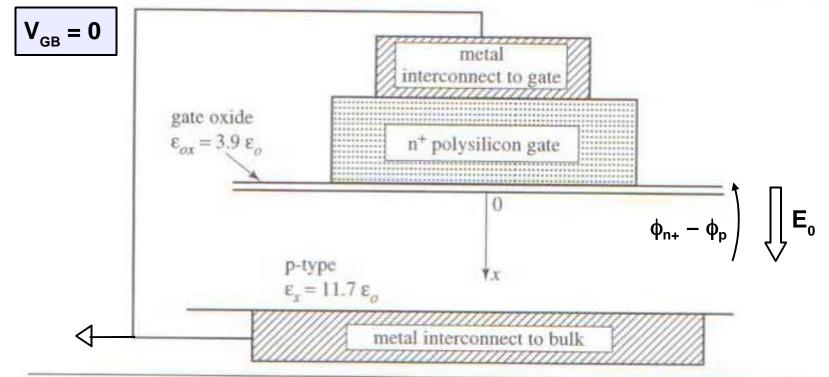

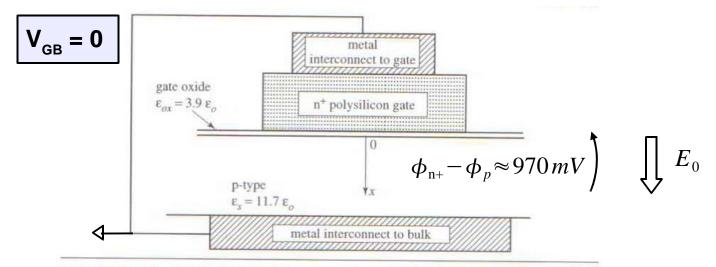

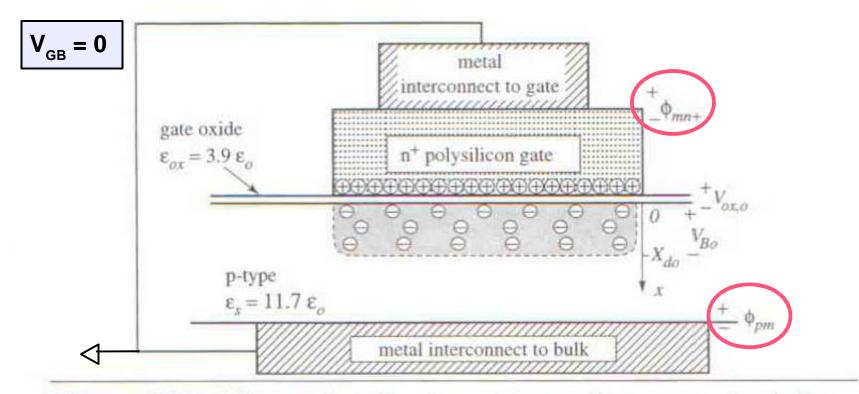

#### MOS structure in Thermal Equilibrium

Figure 3.20 MOS capacitor with p-type substrate. Gate and bulk metal contacts are shorted together for thermal equilibrium.

equilibrium potential in the silicon (bulk=substrate)  $\phi_p = -V_T \ln\left(\frac{N_A}{n_i}\right)$  equilibrium potential in the polysilicon (gate)  $\phi_{n+} = V_T \ln\left(\frac{N_D}{n_i}\right)$  $N_A = 10^{17} cm^{-3}$   $N_D = 3 \cdot 10^{19} cm^{-3}$   $n_i = 10^{10} cm^{-3}$   $\rightarrow \phi_{n+} - \phi_p = 550 \, mV - (-420 \, mV) = 970 \, mV$

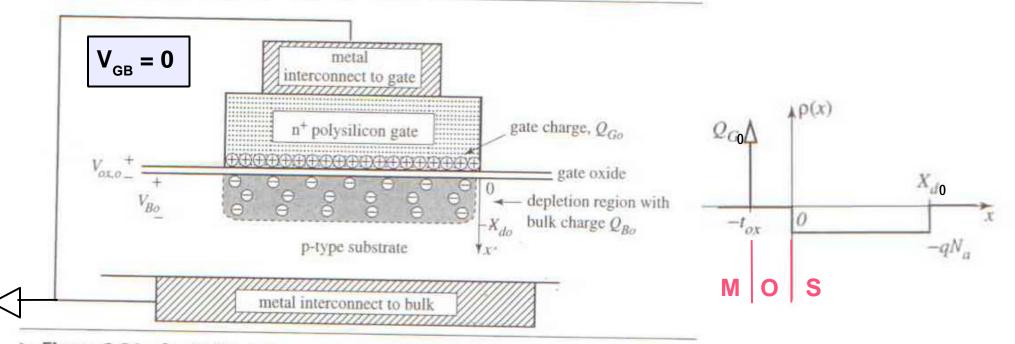

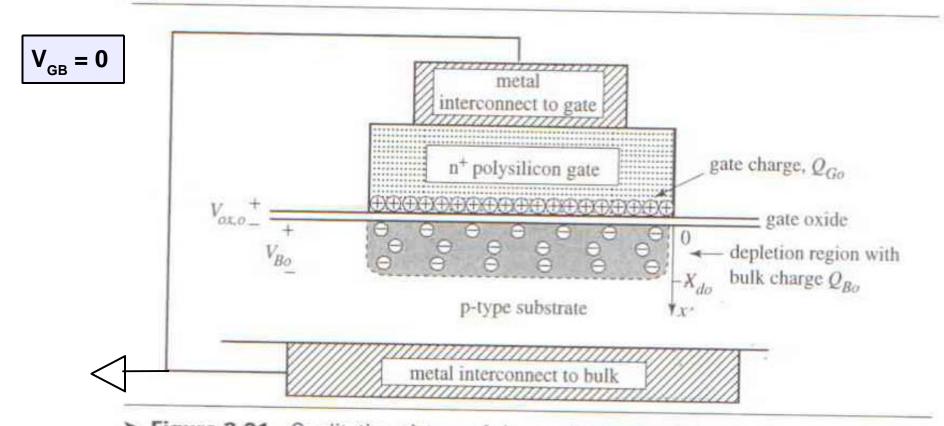

# **MOS in Thermal Equilibrium**

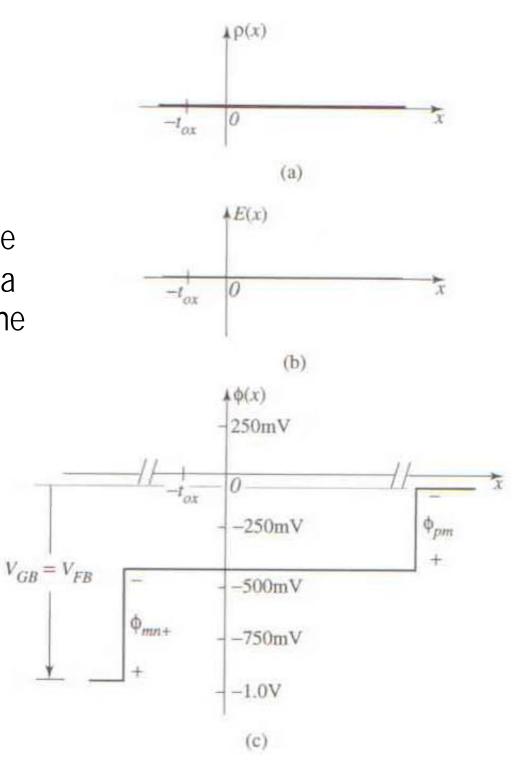

**Figure 3.20** MOS capacitor with p-type substrate. Gate and bulk metal contacts are shorted together for thermal equilibrium.

- From the sign of the potential drop across the MOS structure it follows that the electric field points from gate to bulk.

- Therefore, a positive charge must be present on the polysilicon gate and there must be a balancing negative charge in the p-type silicon substrate (the oxide will be considered a charge-free perfect insulator)

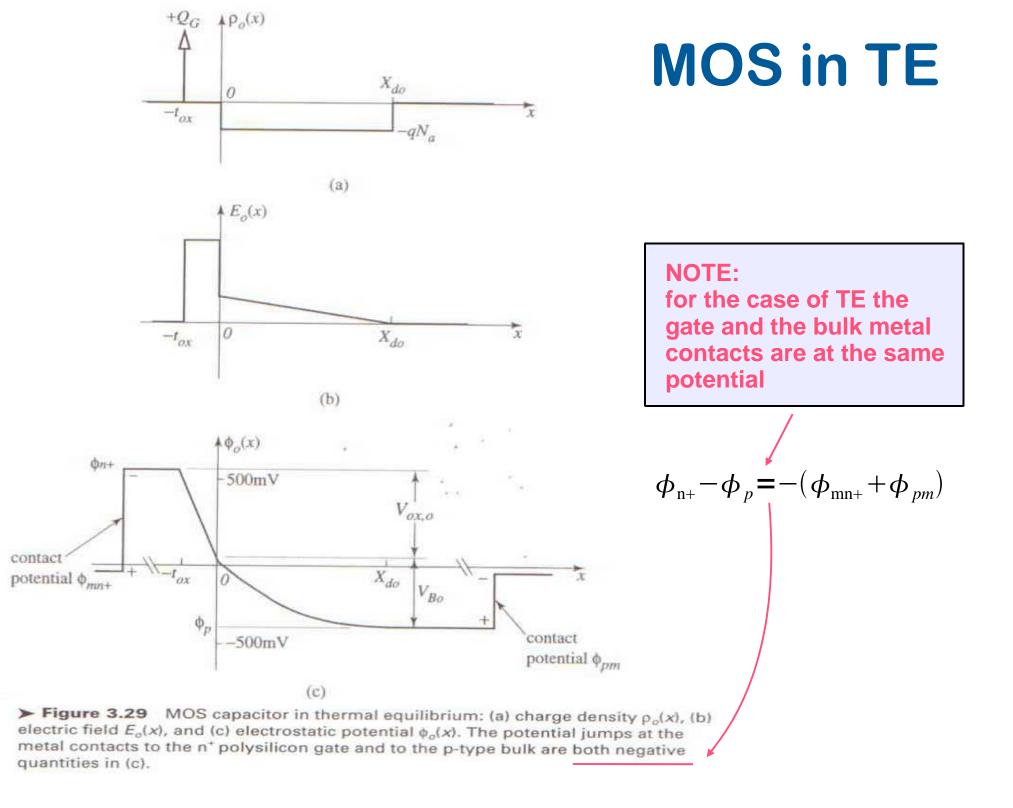

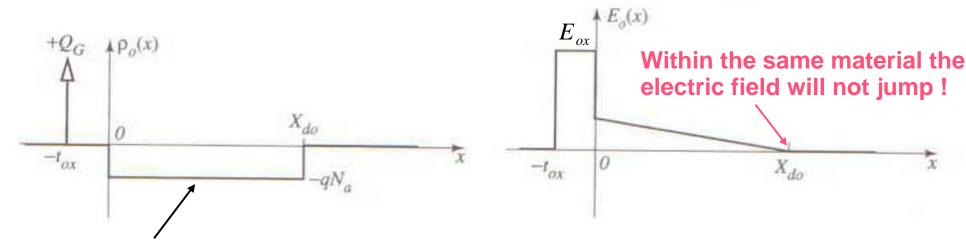

# Charge on the MOS in TE

- Since the gate is highly conductive n+ polysilicon the gate charge Q<sub>G0</sub> can be thought as a sheet charge located at the bottom surface of the polysilicon gate

- The charge on the p-type silicon substrate  $Q_{B0}$  is formed by the immobile negatively charged acceptor ions (to a depletion depth of  $X_{d0}$ ) left behind by the mobile holes repelled by the positive charge on the gate.

► Figure 3.21 Qualitative picture of charge distribution in an MOS capacitor with p-type substrate in thermal equilibrium.

#### Charge on the MOS in TE

Figure 3.21 Qualitative picture of charge distribution in an MOS capacitor with p-type substrate in thermal equilibrium.

$$\mathbf{Q}_{G0} = -\mathbf{Q}_{B0} = q N_A X_{d0} \quad [units: C/cm^2]$$

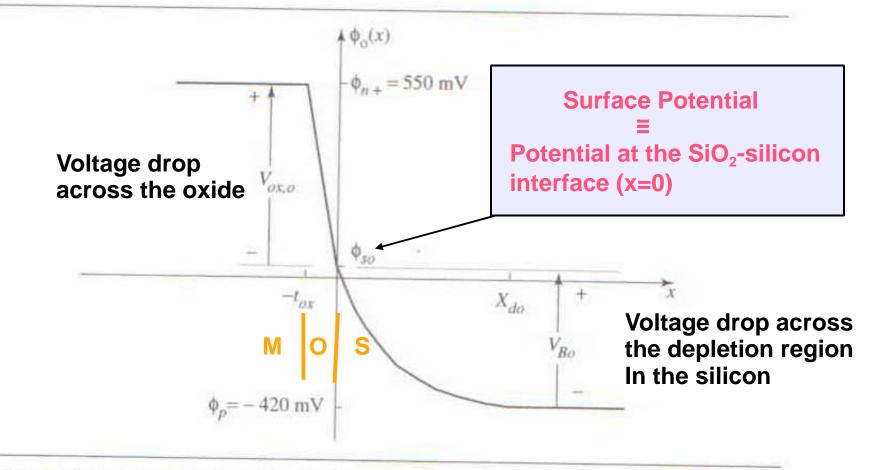

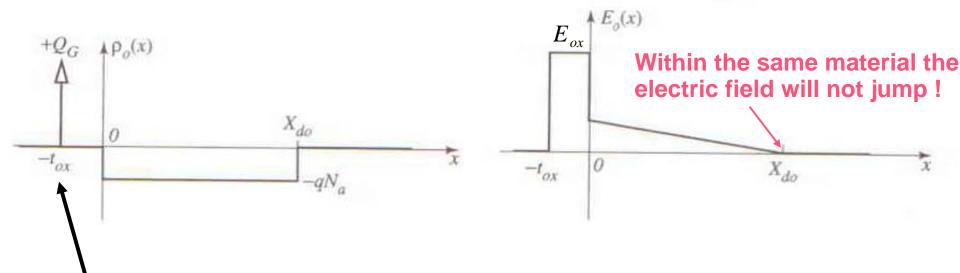

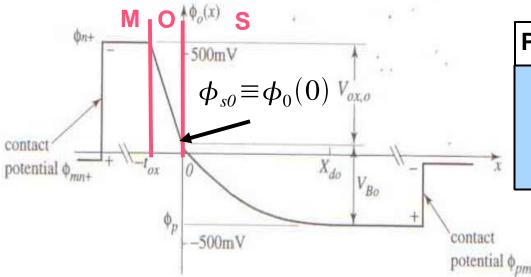

#### Potential across the MOS in TE

Figure 3.22 Potential plot for MOS capacitor with p-type substrate in thermal equilibrium. The substrate doping concentration is  $N_a = 10^{17} \text{ cm}^{-3}$ .

Built in Voltage across  $\phi_{\text{BUILT-IN}} \equiv \phi_{\text{n+}} - \phi_p = V_{ox,0} + V_{B,0}$

#### Potential across the MOS in TE

• The equilibrium potential of a given material is commonly referred as its Fermi potential

$$\phi_{n+} \equiv \phi_{F-\text{gate}} = V_T \ln\left(\frac{N_D}{n_i}\right) \qquad \phi_p \equiv \phi_{F-\text{bulk}} = -V_T \ln\left(\frac{N_A}{n_i}\right)$$

The Built in voltage across the MOS structure is often expressed in term of the work function between the gate material and the bulk silicon

$$-\phi_{MS} \equiv \phi_{\text{F-gate}} - \phi_{\text{F-bulk}} = \phi_{\text{n+}} - \phi_p \equiv \phi_{\text{BUILT-IN}} = V_T \ln\left(\frac{N_D N_A}{n_i^2}\right)$$

NOTE: This term is referred as the metal-to-silicon work function even though the gate terminal is something other than metal (i.e. polysilicon)

### MOS in TE: "fixing" KVL

➤ Figure 3.28 MOS capacitor with p-type substrate, with the charge distribution taken from Fig. 3.21. Gate and bulk metal contacts shorted together for the thermal equilibrium analysis.

$$\phi_{\mathrm{mn+}} + V_{ox,0} + V_{B0} + \phi_{pm} = 0 \quad \longleftrightarrow \quad \underbrace{V_{ox,0} + V_{B0}}_{=(\phi_{\mathrm{n+}} - \phi_{p}) \equiv \phi_{\mathrm{BUILT-IN}}} = (\phi_{\mathrm{mn+}} + \phi_{pm})$$

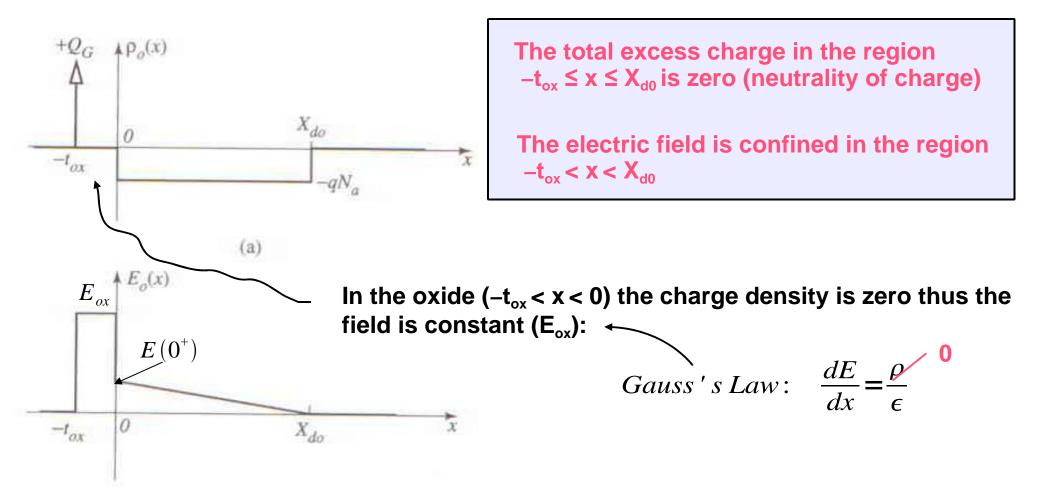

# **MOS in TE: Quantitative Analysis**

Boundary condition at the oxide/silicon interface  $(0 - \le x \le 0 +)$ :

$$\epsilon_{ox} \cdot E_{ox} = \epsilon_{s} \cdot E(0^{+}) \rightarrow E(0^{+}) = \frac{\epsilon_{ox}}{\epsilon_{s}} E_{ox} \rightarrow E_{ox} = E(0^{+}) \frac{\epsilon_{s}}{\epsilon_{ox}}$$

、≈3

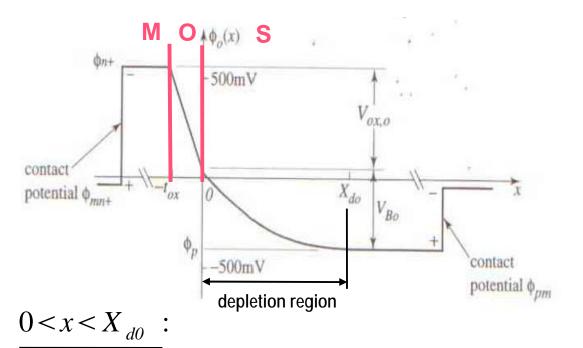

#### **MOS in TE: Quantitative Analysis**

In the charged region of the silicon oxide/silicon interface  $(0+\le x < X_{d0})$  the charge density is constant:

$$dE(x) = \frac{-q N_A}{\epsilon_s} dx \rightarrow \int_{E(0+)}^{E(X_{do})} dE(x) = \frac{-q N_A}{\epsilon_s} \int_{0+}^{X_{do}} dx \rightarrow$$

$$\rightarrow \epsilon_s E(X_{d0}) - \epsilon_s E(0^+) = -q N_A X_{d0} \rightarrow E(0^+) = \frac{q N_A}{\epsilon_s} X_{d0}$$

$$\downarrow$$

$$E_{ox} = E(0^-) = E(0^+) \frac{\epsilon_s}{\epsilon_{ox}} = \frac{q N_A}{\epsilon_{ox}} X_{d0}$$

### **MOS in TE: Quantitative Analysis**

Just for the sake of double-checking the correctness of the previous result let's also apply the boundary condition at the interface between gate and oxide and see if we get the same result

$$\epsilon_{G} \cdot E(-t_{ox}^{-}) + \mathbb{Q}_{G} = \epsilon_{ox} E(-t_{ox}^{+}) \rightarrow \underbrace{E(-t_{ox}^{+})}_{\checkmark} = \frac{\mathbb{Q}_{G}}{\epsilon_{ox}} = \frac{-\mathbb{Q}_{B}}{\epsilon_{ox}} = \frac{q N_{A} X_{d0}}{\epsilon_{ox}}$$

$$= E_{ox}$$

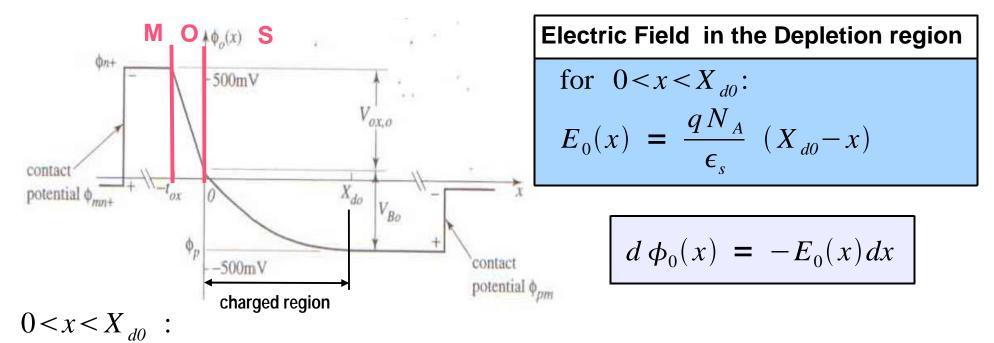

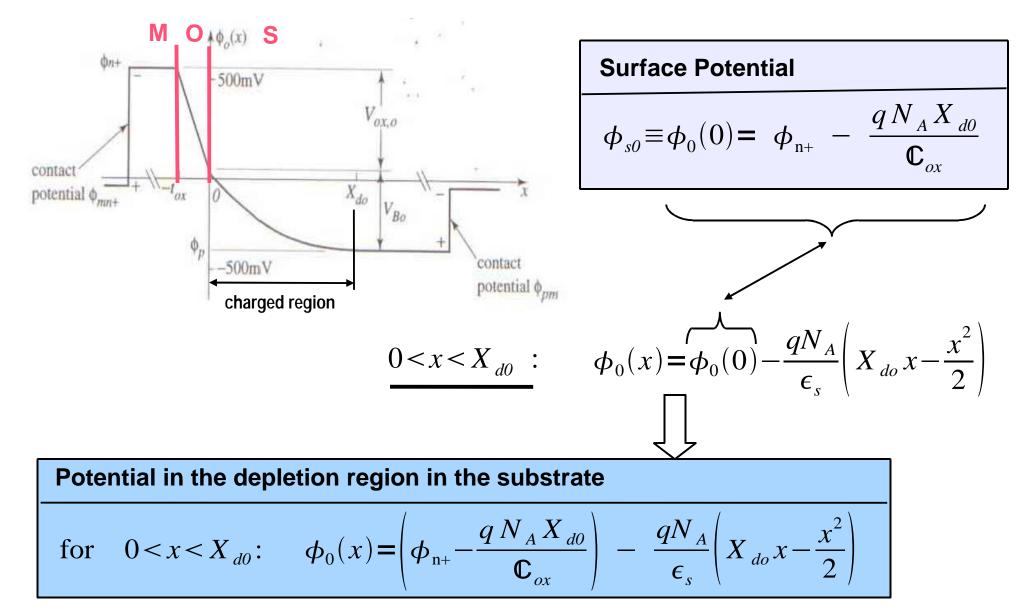

#### **MOS Potential in TE**

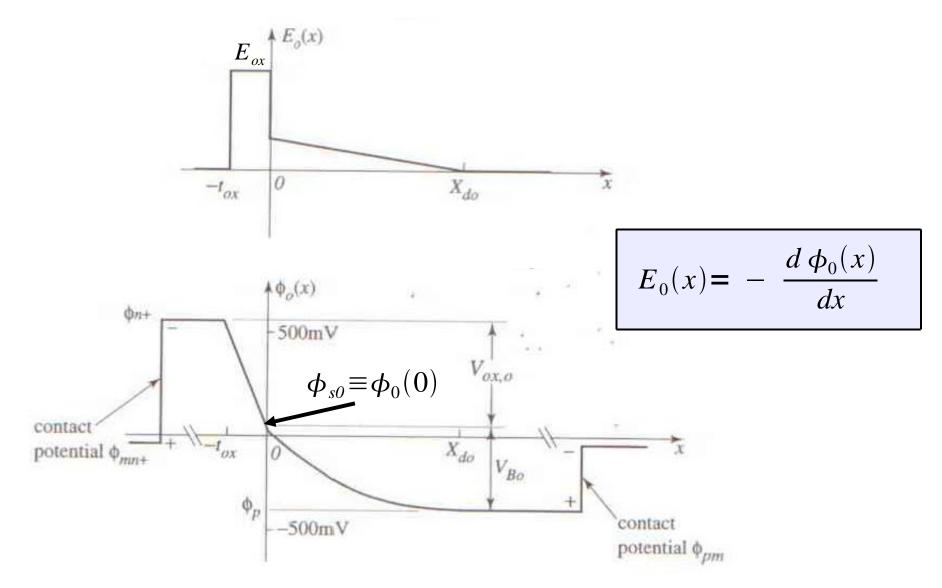

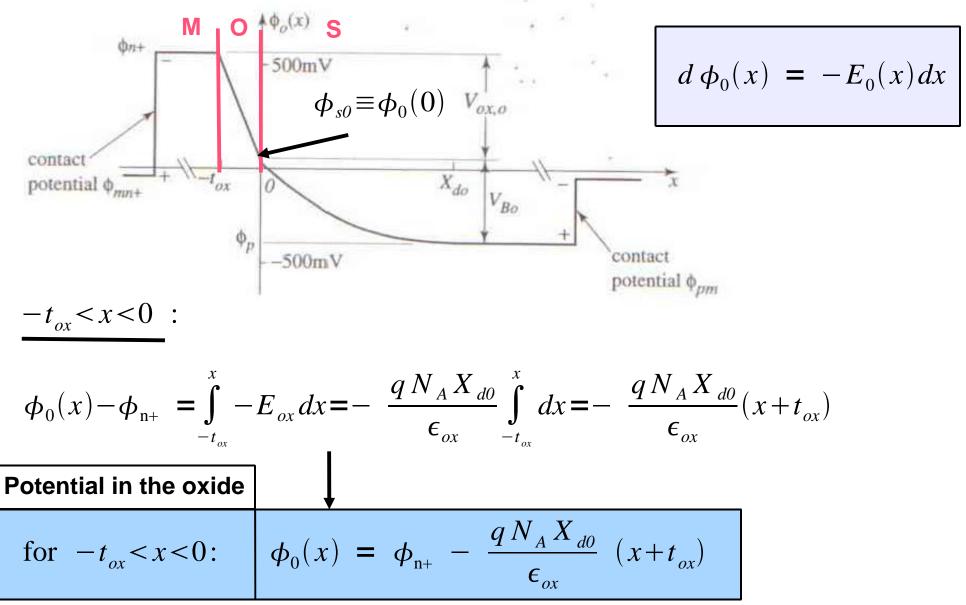

### **MOS in TE: Potential in the oxide**

### MOS in TE: Potential in the oxide

Potential in the oxide

for

$$-t_{ox} < x < 0$$

:

$\phi_0(x) = \phi_{n+} - \frac{q N_A X_{d0}}{\epsilon_{ox}} (x + t_{ox})$

Surface Potential (Potential at the oxide/silicon interface)

$$\phi_{s0} \equiv \phi_0(0) = \phi_{n+} - \frac{q N_A X_{d0}}{\epsilon_{ox}} t_{ox} = \phi_{n+} - \frac{q N_A X_{d0}}{\mathbb{C}_{ox}}$$

with

$$\mathbb{C}_{ox} = \frac{\epsilon_{ox}}{t_{ox}}$$

Voltage drop across the oxide

$$V_{ox,0} \equiv \phi_0(-t_{ox}) - \phi_0(0) = \phi_{n+} - \phi_{s0} = \frac{q N_A X_{d0}}{\mathbb{C}_{ox}} = \frac{\mathbb{Q}_{G0}}{\mathbb{C}_{ox}}$$

with:

$$\mathbf{Q}_{G0} = -\mathbf{Q}_{B0} = q N_A X_{d0}$$

#### NOTE: $V_{ox,0}$ is proportional to the charge stored on each side of the oxide

$$dE_0(x) = \frac{\rho(x)}{\epsilon_s} dx$$

$$\int_{E_0(0+)}^{E_0(x)} dE_0(x) = \int_{0+}^x \frac{\rho(x)}{\epsilon_s} \longrightarrow E_0(x) - E_0(0^+) = \int_{0+}^x \frac{-qN_A}{\epsilon_s} dx = \frac{-qN_A x}{\epsilon_s} \longrightarrow$$

$$E_{0}(x) = E_{0}(0^{+}) - \frac{qN_{A}x}{\epsilon_{s}} = \frac{qN_{A}X_{d0}}{\epsilon_{s}} - \frac{qN_{A}x}{\epsilon_{s}} = \frac{qN_{A}}{\epsilon_{s}} (X_{d0} - x) \longrightarrow$$

$$E_{0}(0^{+}) = \frac{qN_{A}X_{d0}}{\epsilon_{s}}$$

$$\int_{\phi_0(0)}^{\phi_0(x)} d\phi_0(x) = \int_0^x -E_0(x) dx \longrightarrow \phi_0(x) - \phi_0(0) = \int_0^x -\frac{qN_A}{\epsilon_s} (X_{do} - x) dx \longrightarrow$$

$$\phi_0(x) - \phi_0(0) = -\frac{qN_A}{\epsilon_s} X_{do} \int_0^x dx + \frac{qN_A}{\epsilon_s} \int_0^x x dx = -\frac{qN_A}{\epsilon_s} \left( X_{do} x - \frac{x^2}{2} \right) \longrightarrow$$

$$\phi_0(x) = \phi_0(0) - \frac{qN_A}{\epsilon_s} \left( X_{do} x - \frac{x^2}{2} \right) \longrightarrow$$

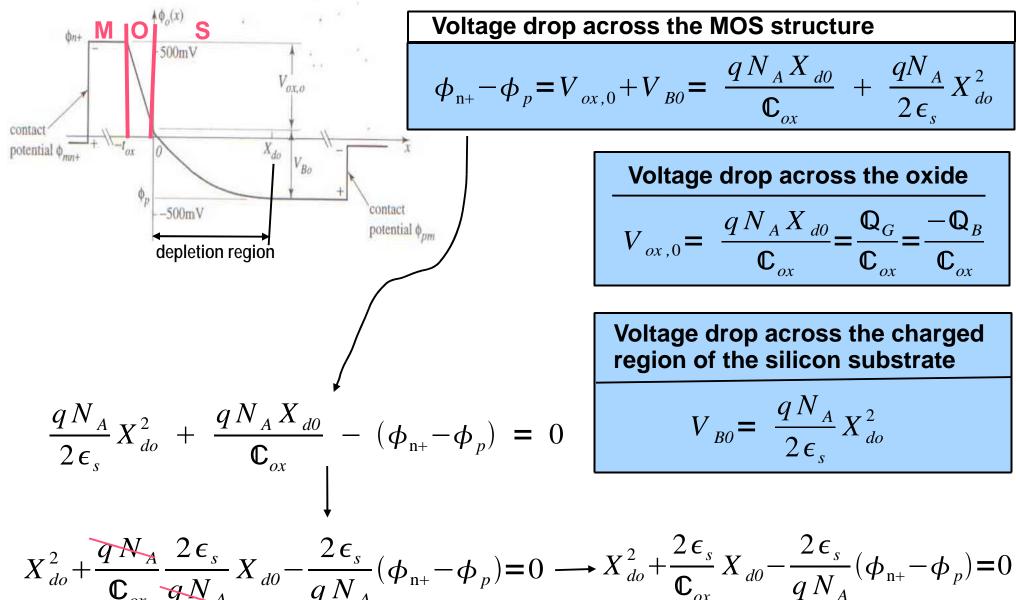

#### MOS in TE: Width of the Depletion region

#### MOS in TE: Width of the Depletion region

$$X_{do}^{2} + \frac{2\epsilon_{s}}{\mathbb{C}_{ox}} X_{d0} - \frac{2\epsilon_{s}}{q N_{A}} (\phi_{n+} - \phi_{p}) = 0$$

$$ax^2+bx+c=0 \longleftrightarrow x=\frac{-b\pm\sqrt{b^2-4ac}}{2a}$$

**NOTE: X<sub>d0</sub> can be only positive**

$$X_{do} = \frac{-2\epsilon_s/\mathbb{C}_{ox} + \sqrt{(4\epsilon_s^2/\mathbb{C}_{ox}^2) + (8\epsilon_s/qN_A)(\phi_{n+} - \phi_p)}}{2} = \frac{-2\epsilon_s/\mathbb{C}_{ox}}{2}$$

$$=-\epsilon_{s}/\mathbb{C}_{ox}+\sqrt{(\epsilon_{s}^{2}/\mathbb{C}_{ox}^{2})+(2\epsilon_{s}/qN_{A})(\phi_{n+}-\phi_{p})}=\frac{\epsilon_{s}}{\mathbb{C}_{ox}}\left(-1+\sqrt{1+\frac{2\epsilon_{s}}{qN_{A}}\frac{\mathbb{C}_{ox}^{2}}{\epsilon_{s}^{2}}(\phi_{n+}-\phi_{p})}\right)$$

$$\downarrow$$

Depletion Width:  $X_{do}=\frac{\epsilon_{s}}{\mathbb{C}_{ox}}\left(\sqrt{1+\frac{2\mathbb{C}_{ox}^{2}}{qN_{A}\epsilon_{s}}(\phi_{n+}-\phi_{p})}-1\right)$

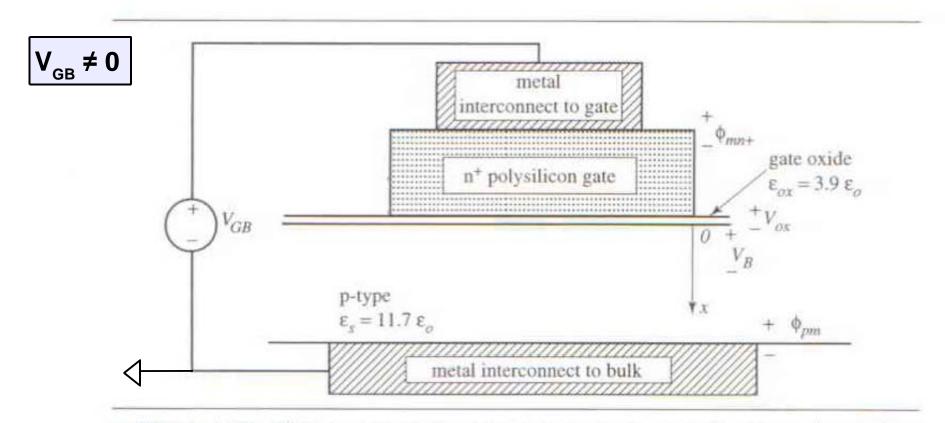

#### **MOS under Bias**

**Figure 3.30** MOS capacitor on a p-type substrate for one-dimensional analysis of charge distribution p(x), electric field E(x), and potential  $\phi(x)$  for the case of an applied bias  $V_{GB}$ .

#### (FLATBAND) – ACCUMULATION – DEPLETION – (THRESHOLD) – INVERSION

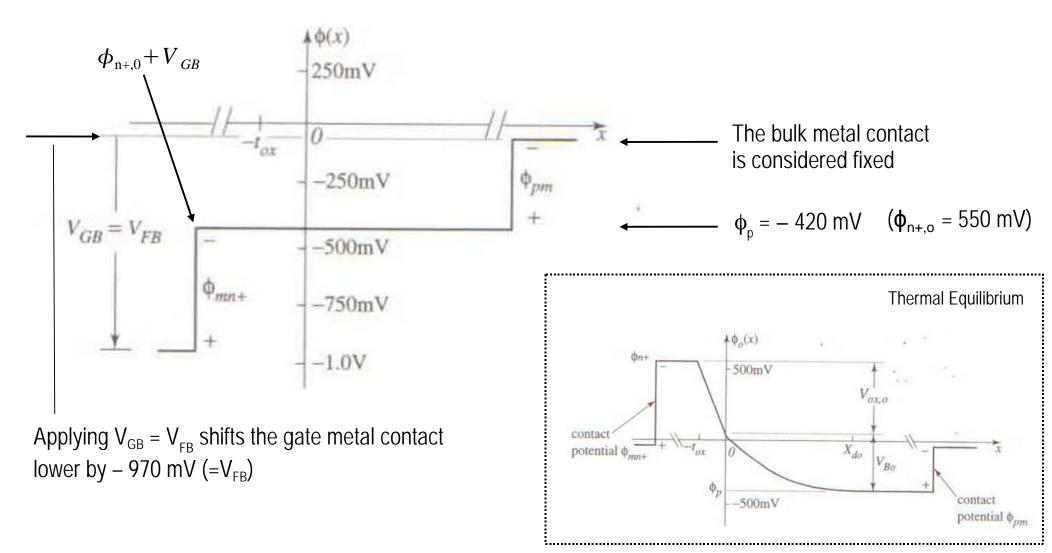

#### Flatband

We apply a gate to bulk voltage that is opposite to the built-in potential. This special voltage bias is called flat-band voltage

$$V_{FB} \equiv -\phi_{\text{BUILT}_{IN}} = -(\phi_{n+.0} - \phi_{p.0})$$

Flat-band Voltage

NOTICE:

For an MOS structure with n+ poly-silicon gate and p-type substrate this voltage is negative

$$V_{GB} = \phi_{mn+} + \phi_{pm} + V_{MOS}$$

$$V_{GB} = \phi_{mn+} + \phi_{pm} + V_{MOS}$$

$$V_{GB} = -\phi_{BUILT-IN} + V_{MOS}$$

$$V_{GB} = -\phi_{BUILT-IN} + V_{MOS}$$

$$V_{GB} = V_{FB} + V_{MOS}$$

#### Flatband

• In flat-band condition ( $V_{GB}=V_{FB}$ ) there is no internal voltage drop across the MOS capacitor.

# Flatband

Since in flat-band condition (V<sub>GB</sub>=V<sub>FB</sub>) there is no internal voltage drop across the MOS capacitor, as a result the electric field is zero and the gate charge density is zero

$$Q_{G}(V_{GB}=V_{FB})=0$$