#### Non Ideal Transistor Behavior

Slides adapted from:

N. Weste, D. Harris, *CMOS VLSI Design*, © Addison-Wesley, 3/e, 2004

#### Non-ideal Transistor I-V effects

- Non ideal transistor Behavior

- Channel Length Modulation

- Threshold voltage effects

- Body effect

- Drain induced Barrier Lowering (DIBL)

- Short Channel effects

- High Field Effects

- Mobility Degradation

- Velocity Saturation

- Leakage

- Sub threshold Leakage

- Gate Leakage

- Junction Leakage

- Process and Environmental Variations

#### **Ideal Transistor I-V**

Schockley long channel transistor model

$$I_{ds} = \begin{cases} 0 & V_{gs} < V_{t} & \text{cutoff} \\ \beta \left(V_{gs} - V_{t} - \frac{V_{ds}}{2}\right) V_{ds} & V_{ds} < V_{dsat} & \text{linear} \\ \frac{\beta}{2} \left(V_{gs} - V_{t}\right)^{2} & V_{ds} > V_{dsat} & \text{saturation} \\ & \& V_{gs} \ge V_{t} \end{cases}$$

$$\beta = \mu \frac{\varepsilon o x}{to x} \frac{W}{L}$$

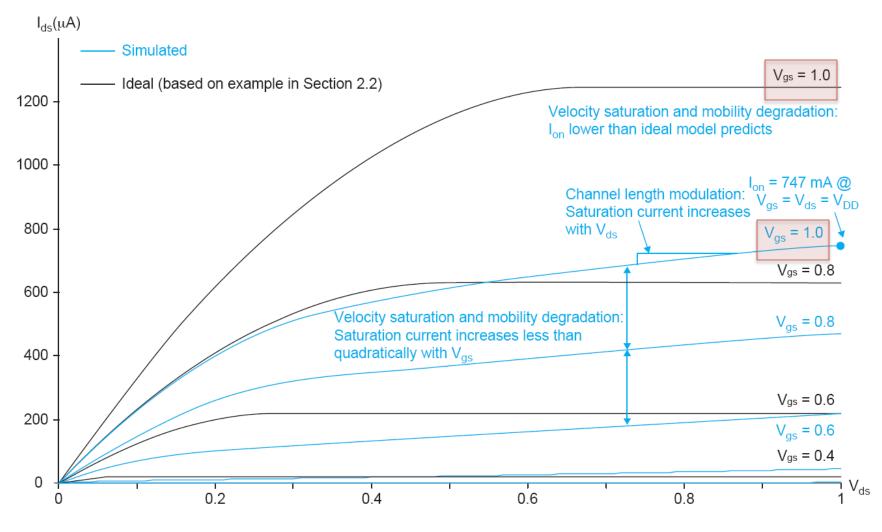

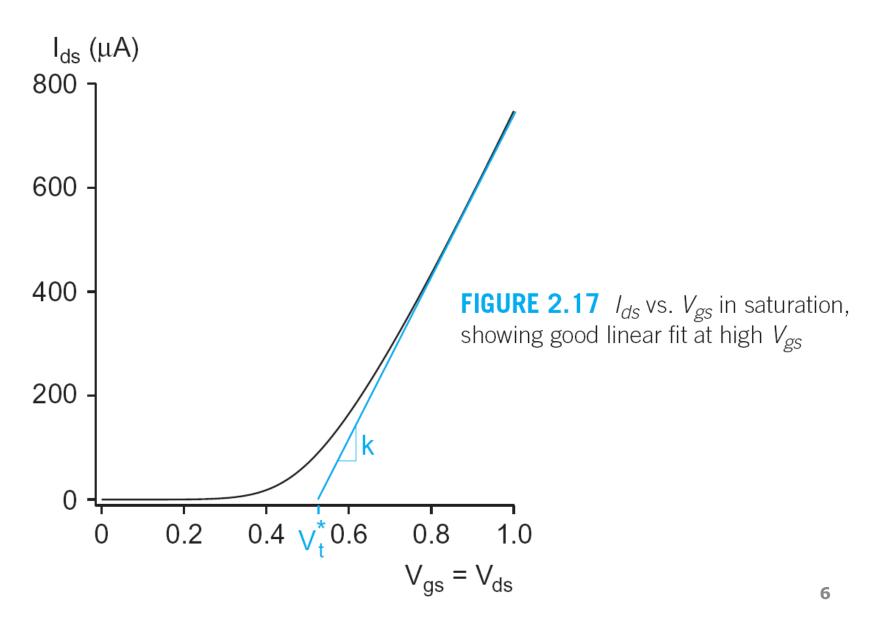

### Ideal vs. Simulated nMOS I-V plots

65 nm IBM process, VDD=1.0V

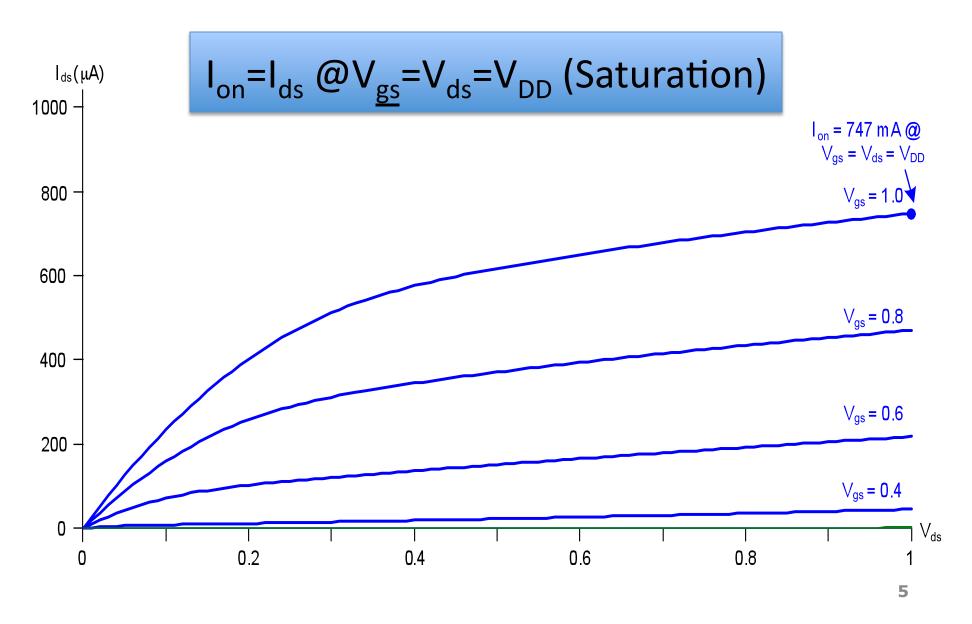

## ON and OFF Current (1/3)

### ON and OFF Current (2/3)

## ON and OFF Current (3/3)

$$I_{off} = I_{ds} @V_{gs} = 0, V_{ds} = V_{DD} (Cutoff)$$

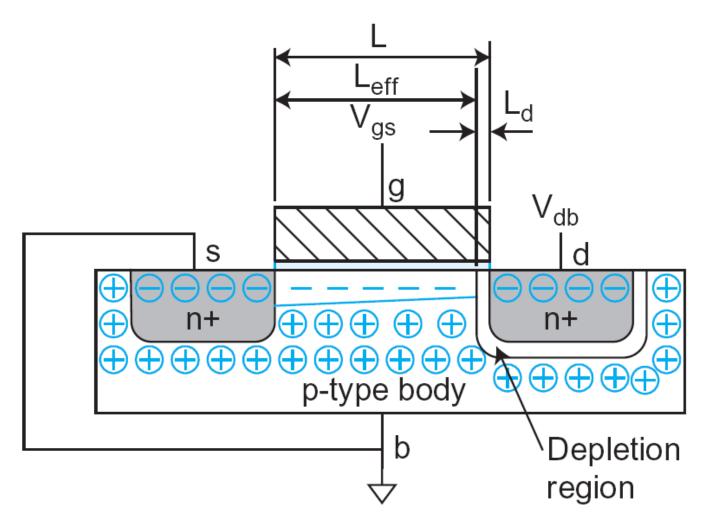

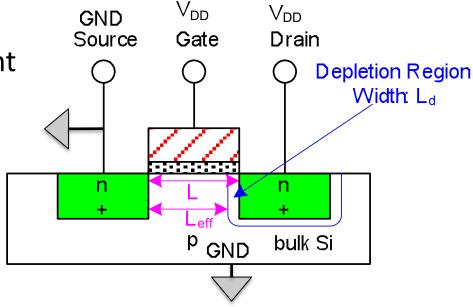

### Channel Length Modulation

FIGURE 2.18 Depletion region shortens effective channel length

### Channel Length Modulation

- Reverse-biased p-n junctions form a depletion region

- Region between n (drain) and p (bulk) with no carriers

- Width of depletion  $L_d$  region (between D and B) grows with reverse bias  $V_{dh}$

$$-L_{eff} = L - L_{d}$$

Shorter L<sub>eff</sub> gives more current

- $-I_{ds}$  increases with  $V_{ds}$

- Even in saturation

### Channel Length Modulation I/V (1/2)

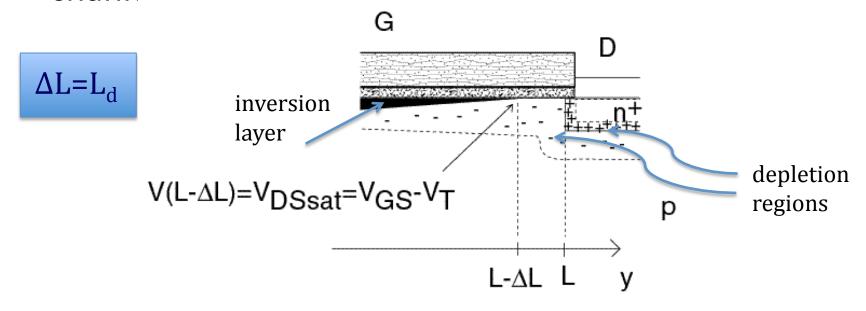

- Increasing  $V_{ds}$  causes the depletion around the drain to widen.

- This pushes the pinch off point further away from the drain resulting in an effective shortening of the channel

### Channel Length Modulation I-V (2/2)

$$I_{ds} \approx \frac{\mu C_{ox}}{2} \cdot \frac{W}{L - \Delta L(V_{ds})} (V_{gs} - V_t)^2$$

$$\approx \frac{\mu C_{ox}}{2} \cdot \frac{W}{L \cdot \left(1 - \frac{\Delta L(V_{ds})}{L}\right)} \cdot (V_{gs} - V_t)^2$$

Taylor's Approx

$$\approx \frac{\mu C_{ox}}{2} \cdot \frac{W}{L} \cdot \left(1 + \frac{\Delta L(V_{ds})}{L}\right) \cdot (V_{gs} - V_t)^2$$

$$\approx \frac{\mu C_{ox}}{2} \cdot \frac{W}{L} \cdot \left(1 + \lambda V_{ds}\right) \cdot \left(V_{gs} - V_{t}\right)^{2}$$

#### Lambda

Lambda is inversely proportional to channel length

$$\lambda \propto \frac{1}{L}$$

- Lambda is a "fudge" factor (do not rely on a precise value of lambda)

- Improved but approximate model for the drain current in saturation:

$$I_{ds} \approx \frac{\mu C_{ox}}{2} \cdot \frac{W}{L} \cdot \left(1 + \lambda V_{ds}\right) \cdot \left(V_{gs} - V_{t}\right)^{2} = \frac{\beta}{2} \cdot \left(1 + \lambda V_{ds}\right) \cdot \left(V_{gs} - V_{t}\right)^{2}$$

#### **Mobility Degradation**

#### **Electric Fields Effects**

- Vertical electric field: E<sub>vert</sub> = V<sub>gs</sub> / t<sub>ox</sub>

- Attracts carriers into channel

- Long channel:  $Q_{channel}$  ∝  $E_{vert}$

- Lateral electric field: E<sub>lat</sub> = V<sub>ds</sub> / L

- Accelerates carriers from drain to source

- Long channel:  $v = \mu E_{lat}$

### **Mobility Degradation**

- High E<sub>vert</sub> effectively reduces mobility

- Collisions with oxide interface (at high  $V_{gs}$ , carriers are buffeted against the oxide interface "wall")

$$\mu_{\text{eff}-n} = \frac{540 \frac{\text{cm}^2}{\text{V} \cdot \text{s}}}{1 + \left(\frac{V_{gs} + V_t}{0.54 \frac{\text{V}}{\text{nm}} t_{\text{ox}}}\right)^{1.85}} \qquad \mu_{\text{eff}-p} = \frac{185 \frac{\text{cm}^2}{\text{V} \cdot \text{s}}}{1 + \frac{\left|V_{gs} + 1.5V_t\right|}{0.338 \frac{\text{V}}{\text{nm}} t_{\text{ox}}}}$$

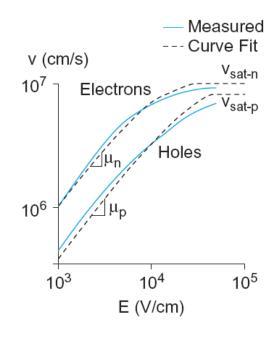

### **Velocity Saturation**

- At high E<sub>lat</sub>, carrier velocity rolls off

- Carriers scatter off (collide) atoms in silicon lattice (at high  $E_{lat}$  the carriers effective mass increases)

- Velocity reaches  $v_{\rm sat}$

- Electrons: 10<sup>7</sup> cm/s

- Holes: 8 x 10<sup>6</sup> cm/s

$$v = \begin{cases} \frac{\mu_{\text{eff}} E}{1 + \frac{E}{E_c}} & E < E_c \\ v_{\text{sat}} & E \ge E_c \end{cases}$$

$$E_c = \frac{2v_{\text{sat}}}{\mu_{\text{eff}}}$$

### Threshold Voltage Effects

- V<sub>t</sub> is the value of V<sub>gs</sub> for which the channel starts to invert

- Ideal models assume V<sub>t</sub> is constant

- In reality it depends (weakly) on almost everything else:

- Body voltage: Body Effect

- Drain voltage: Drain-Induced Barrier Lowering

- Channel length: Short Channel Effect

# Body Effect

$$V_T = V_{T0} + \gamma \cdot \left( \sqrt{\Phi_s - V_{BS}} - \sqrt{\Phi_s} \right)$$

- The potential difference between source and body  $V_{SB}$  affects (increases) the threshold voltage

- Threshold voltage depends on:

$$-V_{SB}$$

$$\gamma = \frac{\sqrt{2q\varepsilon_S N_{bulk}}}{\varepsilon_{ox}/t_{ox}} = Body \quad Effect \quad Coefficient = GAMMA$$

$$\Phi_S = \frac{2KT}{q} \ln \frac{N_{bulk}}{n_i} = Surface \ Potential \equiv PHI$$

The higher the doping  $N_{bulk}$  the more voltage is required to produce an inversion layer:  $N_{bulk} \uparrow \longrightarrow V_T \uparrow$

If  $C_{ox}$  is higher (=  $t_{ox}$  thinner) the less voltage is required to produce an inversion layer (Q=CV):  $C_{ox}$

### **Body Effect**

- V<sub>BS</sub> affect the charge required to invert the channel

- For the same applied  $V_{GS}$ , the application of a negative  $V_{BS}$  (we are only interested in a negative voltage to avoid forward biasing the bulk-to-source pn junction) increases the width of the depletion region, thus the voltage required to invert the channel increases:

$$V_{t} = V_{t0} + \gamma \left( \sqrt{\phi_{s} + V_{sb}} - \sqrt{\phi_{s}} \right)$$

#### DIBL

- So far we assumed the amount of charge in the channel is controlled only by the vertical field

- For short transistors and especially small oxide thickness the amount of charge also depends on the later field. The drain is essentially like another "gate".

- The drain cannot control the charge so well as the gate, but it also affect the amount of charge (and therefore the  $V_t$ )

$$V_t' = V_t - \eta V_{ds}$$

High drain voltage causes current to increase

#### **Short Channel Effect**

- In small transistors the source/drain depletion regions extend into a significant portion of the channel

- impacts the amount of change required to invert the channel

- V<sub>t</sub> typically increases with L (some processes exhibit a reverse short channel effect)

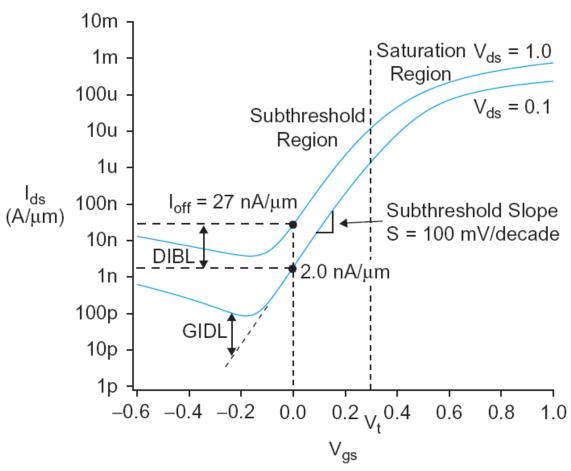

### Leakage

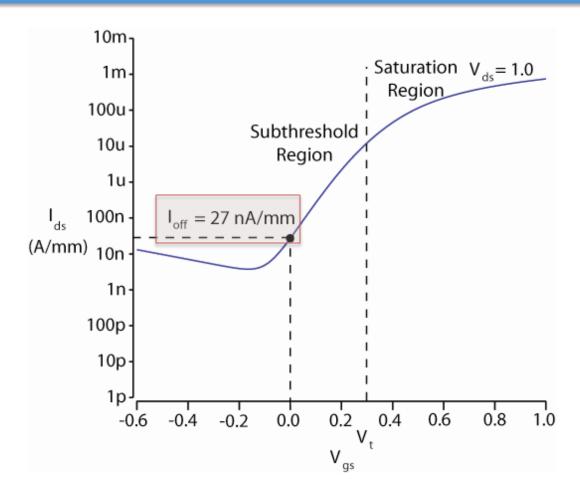

#### What about current in cutoff?

Current doesn't go to 0 in cutoff!!!

**FIGURE 2.20** I-V characteristics of a 65 nm nMOS transistor at 70 °C on a log scale

### Source of Leakage

#### Subthreshold conduction

- Transistors can't abruptly turn ON or OFF

- Dominant source in contemporary transistors

#### Gate leakage

Tunneling through ultrathin gate dielectric

#### Junction leakage

Reverse-biased PN junction diode current

#### Subthreshold Conduction

- In real transistors, current doesn't abruptly cut off below threshold, but rather drop off exponentially with V<sub>GS</sub>

- This leakage current when the transistor is nominally OFF depends on:

$$\begin{array}{lll} - \text{ process } (\epsilon_{\text{ox}}, t_{\text{ox}}) & \rightarrow & \text{hidden in } K_{\gamma} \\ - \text{ doping levels } (N_{\text{bulk}}) & \rightarrow & \text{hidden in } K_{\gamma} \\ - \text{ device geometry (W, L)} & \rightarrow & \text{hidden in } I_{\text{ds0}} \\ - \text{ temperature (T)} & \rightarrow & \text{hidden in } v_{\text{T}} = \text{KT/q} \end{array}$$

- Subthreshold voltage (V<sub>t</sub>)

$$\rightarrow$$

hidden in  $K_{\nu}$

$$\rightarrow$$

hidden in  $v_T = KT/q$

$$I_{ds} = I_{ds0} e^{\frac{V_{gs} - V_{t0} + \eta V_{ds} - k_{\gamma} V_{sb}}{n v_T}} \left(1 - e^{\frac{-V_{ds}}{v_T}}\right)$$

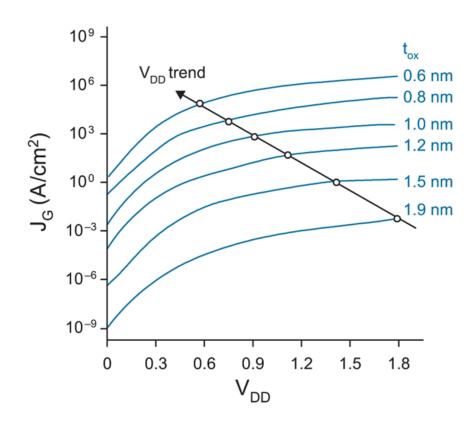

### Gate Leakage

- There is a finite probability that carriers will tunnel through the thin gate oxide.

This result in gate leakage current flowing into the gate.

I<sub>gate</sub> is greater for electrons (nMOS gates leak more)

- The probability drops off exponentially with t<sub>ox</sub>

- For oxides thinner than 15-20 Å, tunneling becomes a critically important factor (at 65nm t<sub>ox</sub>≈10.5 Å)

$$I_{\text{gate}} = WA \left(\frac{V_{DD}}{t_{\text{ox}}}\right)^2 e^{-B\frac{t_{\text{ox}}}{V_{DD}}}$$

A and B are tech constants

FIG 2.20 Gate leakage current from [Song01]

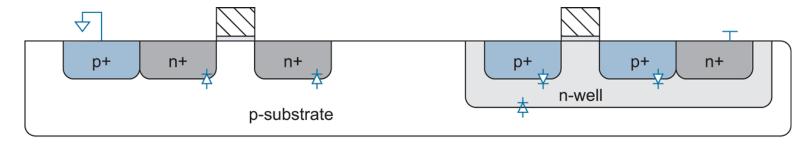

### Junction Leakage

$$I_D = I_S \left( e^{\frac{V_D}{v_T}} - 1 \right)$$

- The p-n junctions between diffusion and the substrate or well for diodes.

- The well-to-substrate is another diode

- Substrate and well are tied to GND and VDD to ensure these diodes remain reverse biased

- But, reverse biased diodes still conduct a small amount of current that depends on:  $(I_S \text{ is typically } < 1fA/\mu m^2)$

- Doping levels

- Area and perimeter of the diffusion region

- The diode voltage

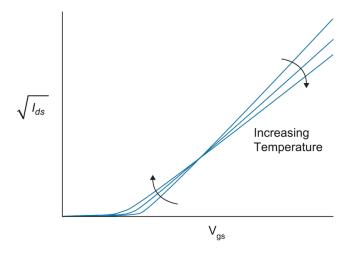

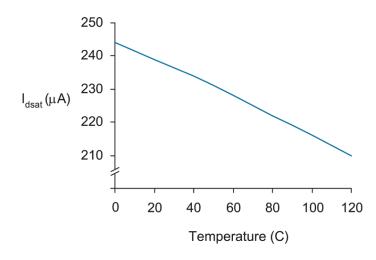

#### Temperature dependence

- Transistor characteristics are influenced by temperature

- $-\mu$  decreases with T

- V<sub>t</sub> decreases linearly with T

- I<sub>leakage</sub> increases with T

- ON current decreases with T

- OFF current increases with T

- Thus, circuit performances are worst at high temperature

FIG 2.21 I–V characteristics of nMOS transistor in saturation at various temperatures

FIG 2.22  $I_{dsat}$  vs. temperature

### Geometry Dependence

- Layout designers draw transistors with W<sub>drawn</sub> L<sub>drawn</sub>

- Actual dimensions may differ from some factor X<sub>W</sub> and X<sub>L</sub>

- The source and drain tend to diffuse laterally under the gate by L<sub>D</sub>, producing a shorter effective channel

- Similarly, diffusion of the bulk by W<sub>D</sub> decreases the effective channel width

- In process below 0.25  $\mu m$  the effective length of the transistor also depends significantly on the orientation of the transistor

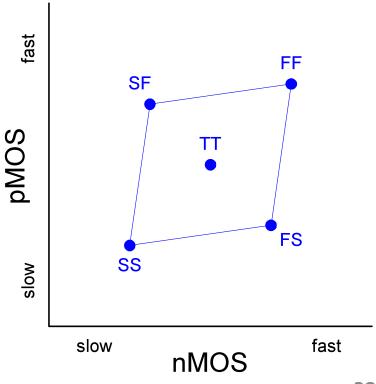

#### **Process Variation**

- Transistors have uncertainty in process parameters

- Process: L<sub>eff</sub>, V<sub>t</sub>, t<sub>ox</sub> of nMOS and pMOS

- Variation is around typical (T) values

- Fast (F)

- L<sub>eff</sub>: short

- $-V_{t}$ : low

- $-t_{ox}$ : thin

- Slow (S): opposite

- Not all parameters are independent for nMOS and pMOS

#### **Environmental Variation**

- $V_{DD}$  and Temperature also vary in time and space

- Fast:

$-V_{DD}$ : high

- T: low

| Corner | Voltage Temperature |       |

|--------|---------------------|-------|

| F      | 1.98                | 0 C   |

| Т      | 1.8                 | 70 C  |

| S      | 1.62                | 125 C |

#### **Process Corners**

- Process corners describe worst case variations

- If a design works in all corners, it will <u>probably</u> work for any variation.

- Describe corner with four letters (T, F, S)

- nMOS speed

- pMOS speed

- Voltage

- Temperature

### **Important Corners**

• Critical Simulation Corners include

| Purpose              | nMOS | pMOS | V <sub>DD</sub> | Temp |

|----------------------|------|------|-----------------|------|

| Cycle time           | S    | S    | S               | S    |

| Power                | F    | F    | F               | F    |

| Subthreshold leakage | F    | F    | F               | S    |

### Impact of non-ideal I-V effects

- Threshold is a significant fraction of the supply voltage

- Leakage is increased causing gates to

- consume power when idle

- limits the amount of time that data is retained

- Leakage increases with temperature

- Velocity saturation and mobility degradation result in less current than expected at high voltage

- No point in trying to use high VDD to achieve fast transistors

- Transistors in series partition the voltage across each transistor thus experience less velocity saturation

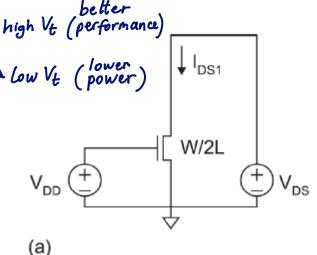

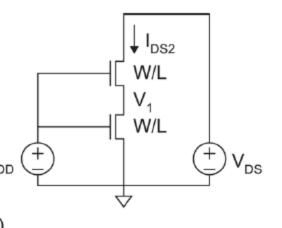

- Tend to be a little faster than a single transistor V<sub>DD</sub>

- Two nMOS in series deliver more than half the current of a single nMOS transistor of the same (b) width

FIG 2.37 Current in series transistors

- Matching: same dimension and orientation

#### So What?

- So what if transistors are not ideal?

- They still behave like switches.

- But these effects matter for...

- Supply voltage choice

- Logical effort

- Quiescent power consumption

- Pass transistors

- Temperature of operation