## **Problem Set**

## Problem

Assume you got a new technology file for SPICE, so you need to do some hand calculations and related SPICE simulations to confirm what to expect from the technology at hand.

1. Assume a W=40 $\mu$ m and L=1.6 $\mu$ m NMOS device, with KP=50 $\mu$ A/V², VTO=0.5V and COX=2.3mF/m² and use the following lambda scaling rule:

$$\lambda(L) = \frac{0.1 \ \mu m \cdot V^{-1}}{L}$$

For a bias current of 0.25mA and assumed Vds=2.5V, compute (by hand) the required Vgs and resulting Cgs as well as small-signal gm and gds (ignoring all extrinsic capacitances).

- 2. Now compute by hand all extrinsic capacitances. Assume that CGSO=0.5nF/m and CGDO=0.5nF/m. The junction capacitances are specified by the formulae given in Table 1. Table 1 also provides all needed HSPICE parameters. Compute the resulting Cgd, Cgs, Cjdb, Cjsb values (use Ldiff=3µm).

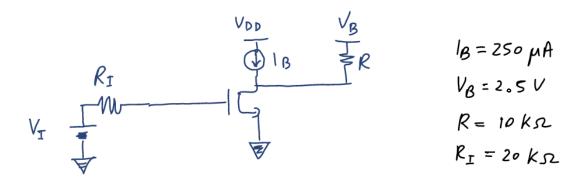

- 3. Construct an HSPICE deck, to be used for finding out the dc operating point and ".op" output for the circuit of figure 1. Use R=10K $\Omega$ , Ri=20K $\Omega$ , VDD=5V, VB=2.5V, IB=250 $\mu$ A and the model formulation shown in table 2. Run the simulations and confirm your hand calculations in part 1. and 2. (These should be virtually identical to your hand calculations). State exactly how you arrive at the total nodal values provided by SPICE, starting from your results in 1. and 2. Your homework solution must include both your input and output files (Make sure to correctly specify VI to get Vds=2.5V).

Table 1.

| Parameter | Purpose                         | nMOS                    |

|-----------|---------------------------------|-------------------------|

| KP        | μCox                            | 50uA/V <sup>2</sup>     |

| COX       | εοx/tox                         | 2.3fF/um <sup>2</sup>   |

| VTO       | Threshold Voltage               | 0.5V                    |

| LAMBDA    | Channel Length Modulation       | 0.1V <sup>-1</sup> um/L |

| CGDO,CGSO | Gate-drain, gate-source overlap | 0.5fF/um                |

|           | capacitance                     |                         |

| CJ        | Zero Bias area capacitance      | 0.1fF/um <sup>2</sup>   |

| CJSW      | Zero bias sidewall capacitance  | 0.5fF/um                |

| PB        | Junction potential              | 0.95V                   |

| MJ        | Area junction grading           | 0.5                     |

|           | coefficient                     |                         |

| MJSW      | Sidewall junction grading       |                         |

|           | coefficient                     | 0.33                    |

| HDIF      | Half length of S/D diffusion    | 1.5um                   |

|           | (Ldiff/2)                       |                         |

| GAMMA     | Bulk threshold voltage          | $0.6  V^{1/2}$          |

| PHI       | Surface Potential               | 0.8V                    |

$$Cjdb = \frac{AD \cdot CJ}{\left(1 + \frac{VDB}{PB}\right)^{MJ}} + \frac{PD \cdot CJSW}{\left(1 + \frac{VDB}{PBSW}\right)^{MJSW}}$$

$$Cjsb = \frac{AS \cdot CJ}{\left(1 + \frac{VSB}{PB}\right)^{MJ}} + \frac{PS \cdot CJSW}{\left(1 + \frac{VSB}{PBSW}\right)^{MJSW}}$$

Table 2.

```

.param lambda=0.1u

.param Ln=1.6u

.model my_nmos nmos kp=50u vto=0.5 lambda='lambda/Ln' cox=2.3e-3 capop=1

+ cgdo=0.5n cgso=0.5n cj=0.1m cjsw=0.5n pb=0.95 mj=0.5 pbsw=0.95

+ mjsw=0.33 gamma=0.6 phi=0.8

+ acm=3 cjgate=0 hdif=1.5u

```

Figure 1.

## Write a short report including:

- 1. Hand calculation (state clearly any assumption you make)

- 2. Hspice input and output files

- 3. Table showing hand calculation and SPICE results. Explain the discrepancy.

- 4. State exactly how you arrive at the total nodal values provided by SPICE, starting from your hand calculation results.