# Digital Systems: Quick Review

## **Digital System**

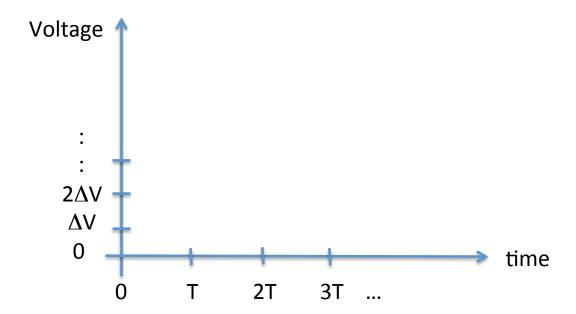

Transform signals that can be abstracted as discrete in range and domain

# Analog & (vs.) Digital

- Analog Circuits Advantages

- Require less devices

- Better to deal with low signal amplitudes

- Better to deal with high frequencies

- Digital Circuits Advantages

- More "adaptable" (e.g. microprocessor)

- Design can be done at a more abstract level

- Better economic

## Types of Digital Circuits

#### Combinational

The value of the outputs at any time t depends only on the combination of the values applied at the inputs at time t (the system has no memory)

#### Sequential

The value of the outputs at any time t depends not only on the values applied at the inputs at time t but also on the past sequence of inputs that have been applied to it (system with memory)

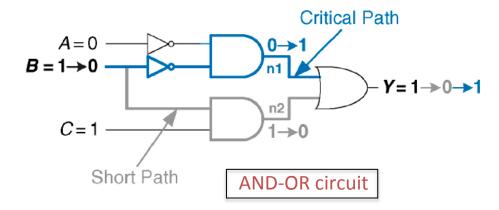

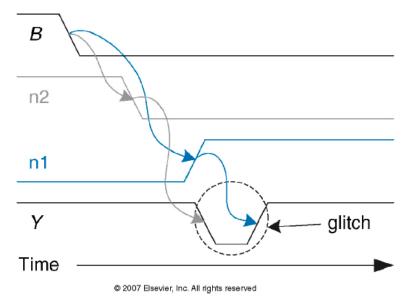

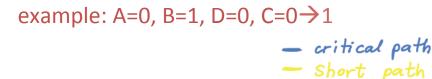

## C.L.: effect of gate delays

- The analysis of combinational circuits ignoring delays can predict only the steady-state behavior of a circuits. That is they predict a circuit's output as a function of its inputs under the assumption that the inputs have been stable for a long time, relative to the delays into the circuit's electronics.

- Because of circuit delays, the transient behavior of a combinational logic circuit may differ from what is predicted by a steady-state analysis.

- In particular a circuit's output may produce a short pulse (often called a glitch) at a time when steady state analysis predicts that the output should not change.

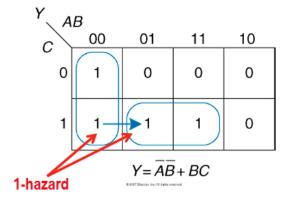

## C.L.: Timing Hazards

- A glitch is an unwanted pulse at the output of a combinational logic network – a momentary change in an output that should not have changed.

- A circuit with the potential for a glitch is said to have a hazard.

- An hazard is something intrinsic about a circuit; a circuit with hazard may or may not have a glitch depending on input patterns and the electric characteristics of the circuit.

#### When do C.L. circuits have Hazards?

Hazards are potential unwanted transients that occur in the output when different paths from input to output have different propagation delays

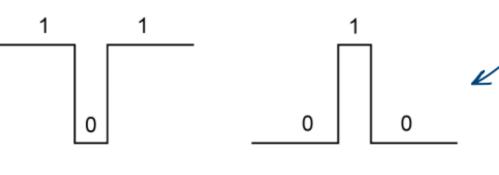

# Types of Hazards (on an output)

The output undergoes a momentary transition when it is expected to remain unchanged

(a) Static 1-hazard

(b) Static 0-hazard

The output changes multiple times as the result of a single input transition

(c) Dynamic hazards

#### **Detection of Static 1-Hazards**

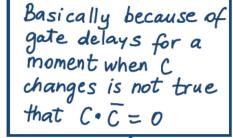

Basically because of gate delays for a moment when B changes is not true that B+B=1

Temporary violation of complementary law.

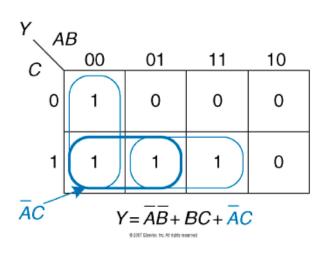

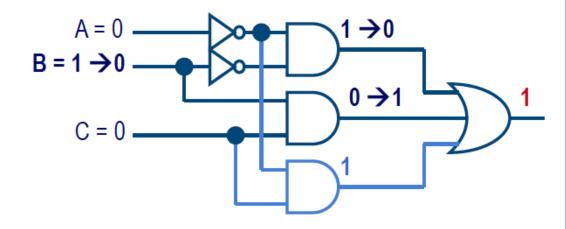

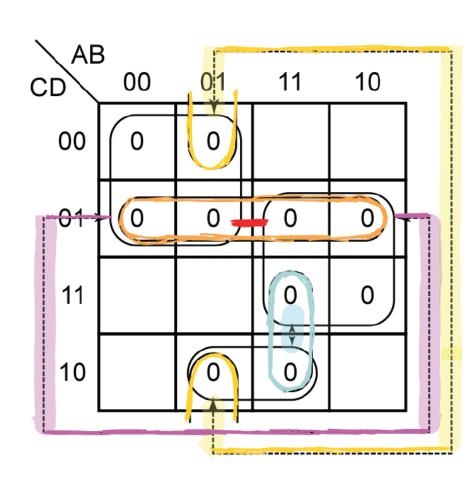

## Removing Static Hazards

• The fundamental strategy for eliminating an hazard is to add redundant prime implicants (extra prime implicants won't change F, but can cause F to be asserted independently of the change to the input that cause the hazard).

circuit with hazard removed

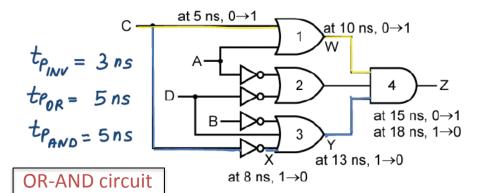

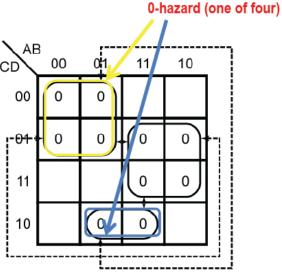

#### Detection of static 0-Hazards

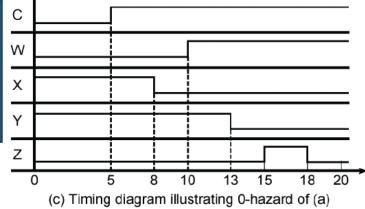

(a) Circuit with a static 0-hazard

(b) Karnaugh map for circuit of (a)

Temporary violation of complementary law

$F = \frac{(A+C)}{(\bar{A}+\bar{D})}.$   $(\bar{B}+\bar{C}+\bar{D})$

## Removing Static Hazards

The circuit has

4 potential

sources of

hazards

that must be

removed

$$F = (A+C) \cdot (\overline{A}+\overline{D}) \cdot (\overline{B}+\overline{C}+D) \cdot (C+\overline{D}) \cdot (A+\overline{B}+D) \cdot (\overline{A}+\overline{B}+\overline{C})$$

# In theory: we need to focus only on one type of hazard!

- A properly designed two level AND-OR circuit has no static 0-hazards. A static 0-hazard would exist only if both a variable and its complement were connected to the same AND gate, which would be a nonsense (A·A'·X=0)

- A properly designed two level OR-AND circuit has no static 1-hazards. A static 1-hazard would exist only if both a variable and its complement were connected to the same OR gate, which would be a nonsense (A+A'+X=1)

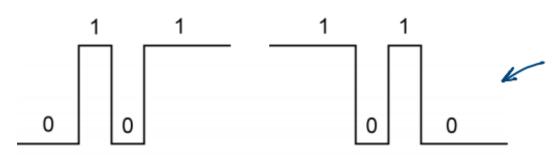

## Dynamic Hazards

- If there are 3 or more paths from an input or its complement to the output the circuit has the potential for a dynamic hazard.

- Three or more paths from an input or its complement to the output can exist only in a multi-level networks. This means that dynamic hazards do not occur in a properly designed two level AND-OR or OR-AND network.

- Analysis and elimination of dynamic hazards is a rather complicated process.

- If you need a hazard free network, it is best to use a 2-level network and use the techniques shown earlier to eliminate the static hazards.

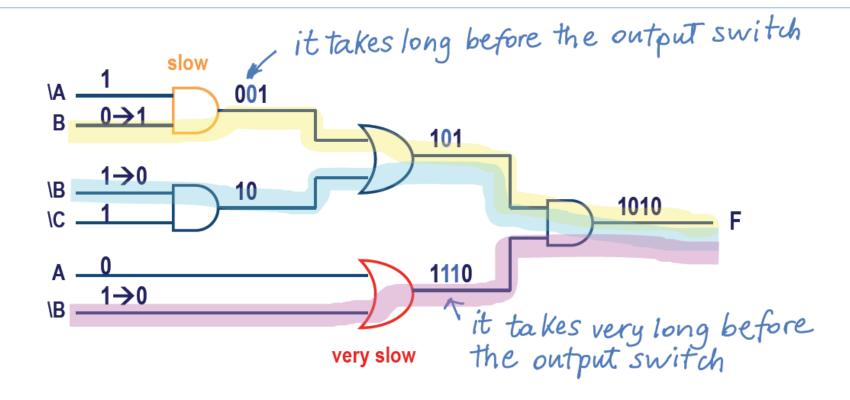

#### Dynamic Hazard Example

All gates are ideal (very fast) except a slow AND gate and a very slow OR gate

#### Hazard-Free Design

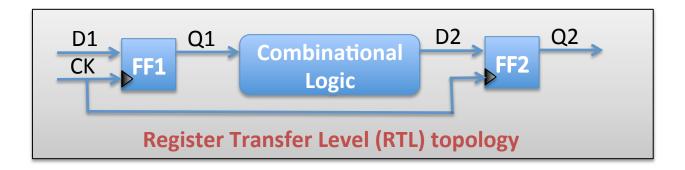

- Best way to deal with hazards: structure the design so that you do not have to worry about them !!!

- A well-designed, synchronous digital system is structured so that hazard analysis is not needed

• In a synchronous system, all the inputs to a combinational circuit are changed at a particular time, and the outputs are not looked at until they have time to settle to a steady-state value.

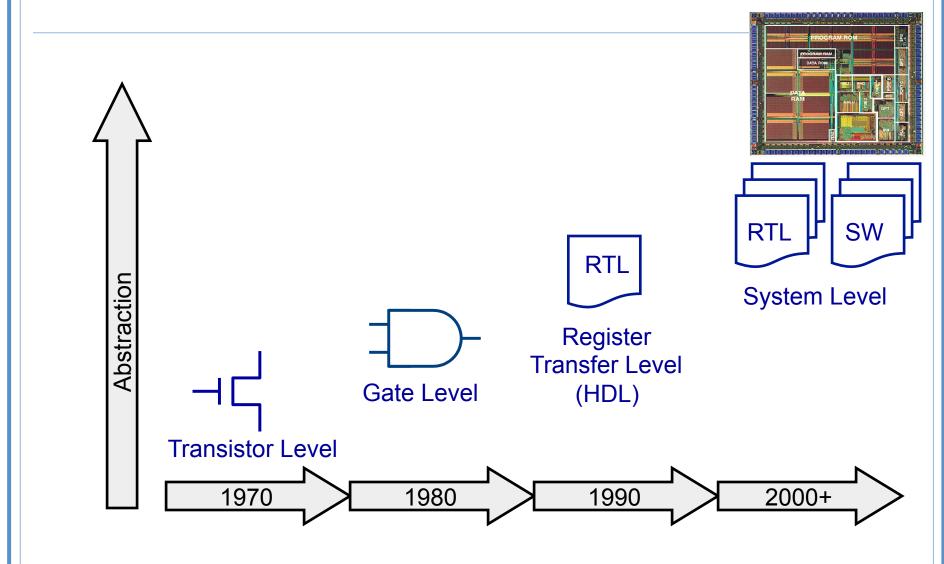

# Timing Issues in S.L. circuits

- Set-up Time

- Hold Time

- Clock skew

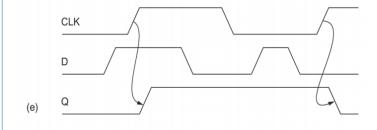

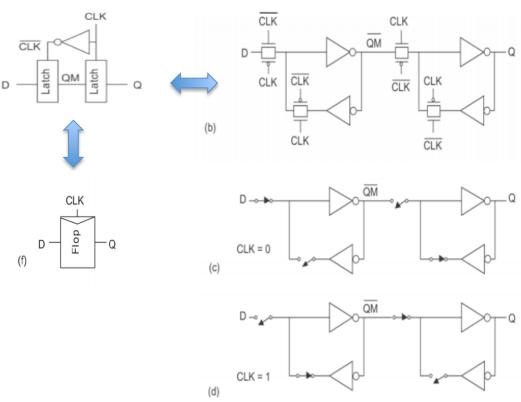

FIG 1.31 CMOS positive-edge-triggered D flip-flop

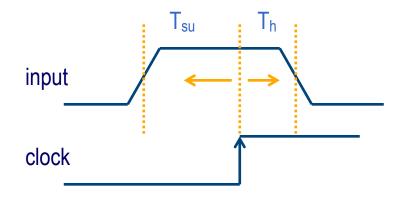

## Setup/Hold Time

- An input to a flip flop can be validly recognized only if:

- it is stable before the clocking event for a minimum time interval T<sub>setup</sub> and

- it is stable after the clocking event for a minimum time interval T<sub>hold</sub>

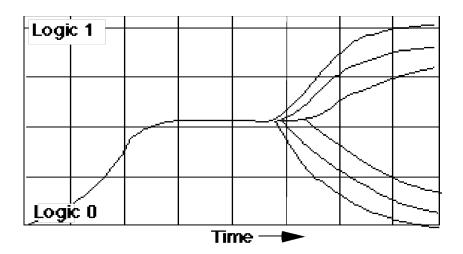

## Setup/Hold Time Violation

- It is dangerous to allow input signals to change very close to the sampling event (that is the active clock edge)

- If setup or hold time constraints are not satisfied, the input maybe interpreted as a 1 or a 0 or some unrecognizable value between 0 and 1 (metastable value)

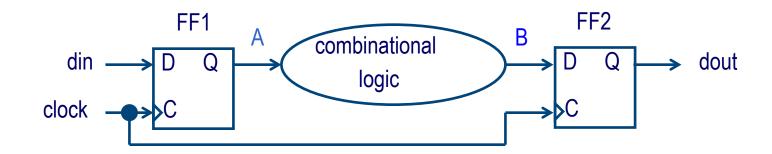

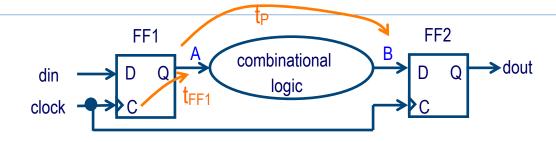

#### Timing Constraints in S.L. circuits

Let's assume din is applied in a way that satisfies setup and hold time for FF1, and let's examine what happen to FF2

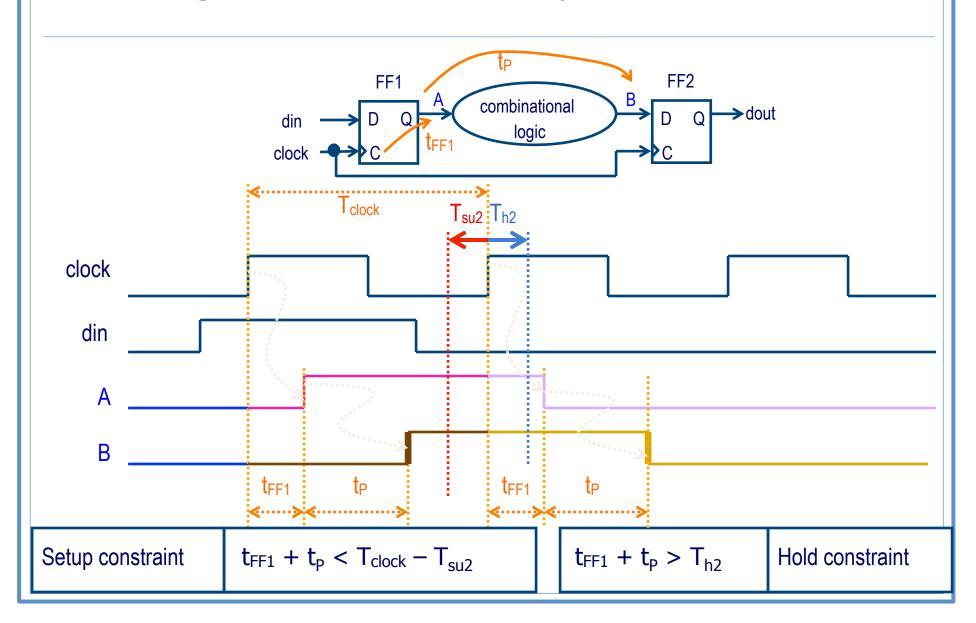

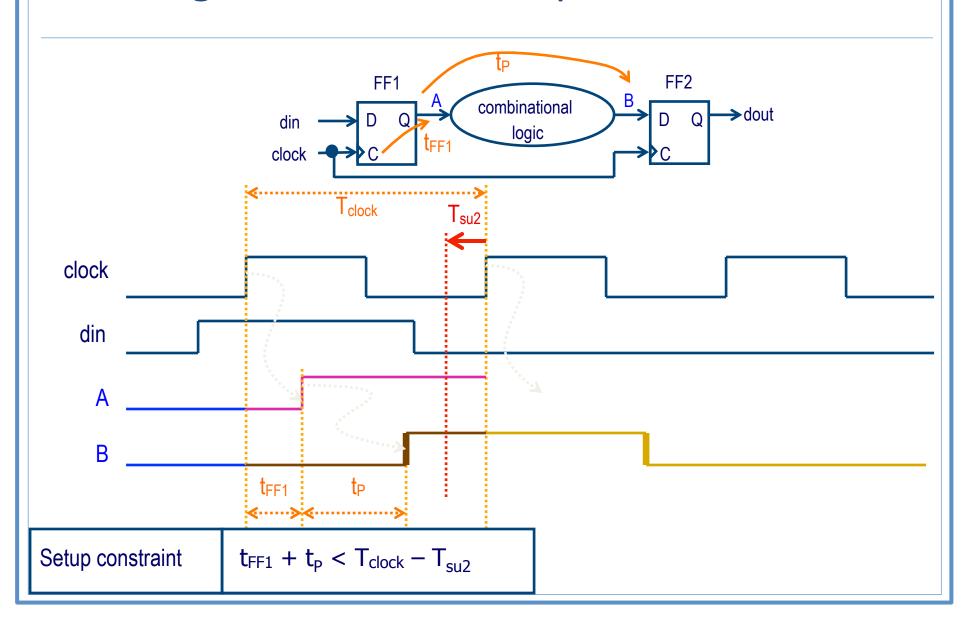

#### Timing constraints in sequential circuits

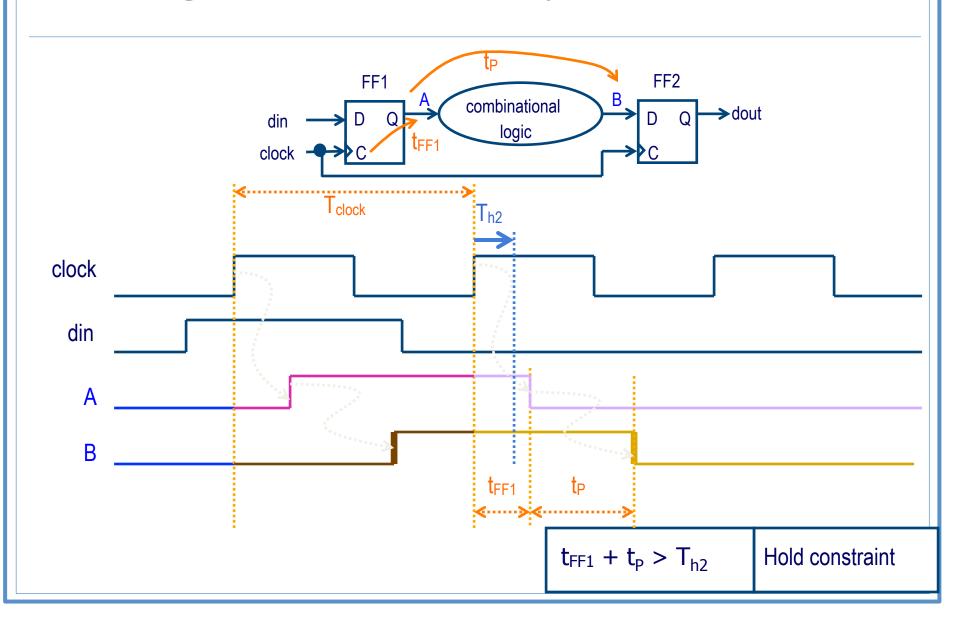

#### Timing constraints in sequential circuits

#### Timing constraints in sequential circuits

#### Max/Min delays

Setup constraint  $t_{FF1} + t_P < T_{clock} - T_{su2}$

$t_{FF1} + t_P > T_{h2} \qquad H$

Hold constraint

- Unfortunately, delays through gates are not constant. Delays change with:

- Supply Voltage, Temperature, and Manufacturing Process

- Setup constraint is more difficult to satisfy when delays are max (V<sub>DD</sub>↓, T↑, P↑)

- Hold constraint is more difficult to satisfy when delays are min  $(V_{DD}\uparrow, T\downarrow, P\downarrow)$

$$-$$

$V_{DD} \downarrow \rightarrow V_{gs} \downarrow \rightarrow I_{ds} \downarrow \rightarrow it takes longer to charge <math>C_L$

$T \uparrow \rightarrow \mu \downarrow \rightarrow \beta \downarrow \rightarrow I_{ds} \downarrow \rightarrow$  it takes longer to charge  $C_L$

$$Ids = \beta(Vgs - VT)^2$$

#### Minimum Clock period for a Sequential circuit

max frequency at which the circuit can

Minimum clock period (t<sub>clk</sub>)

#### Minimum Clock Period for a Sequential Circuit

make sure to compute it with max delays

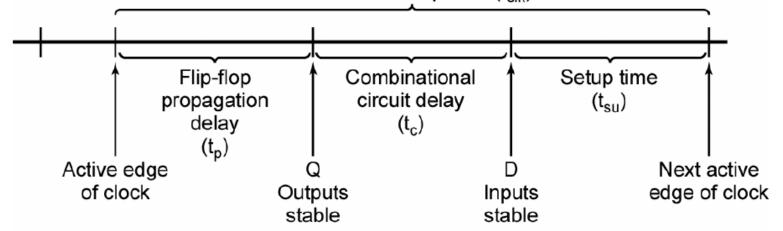

#### Clock skew

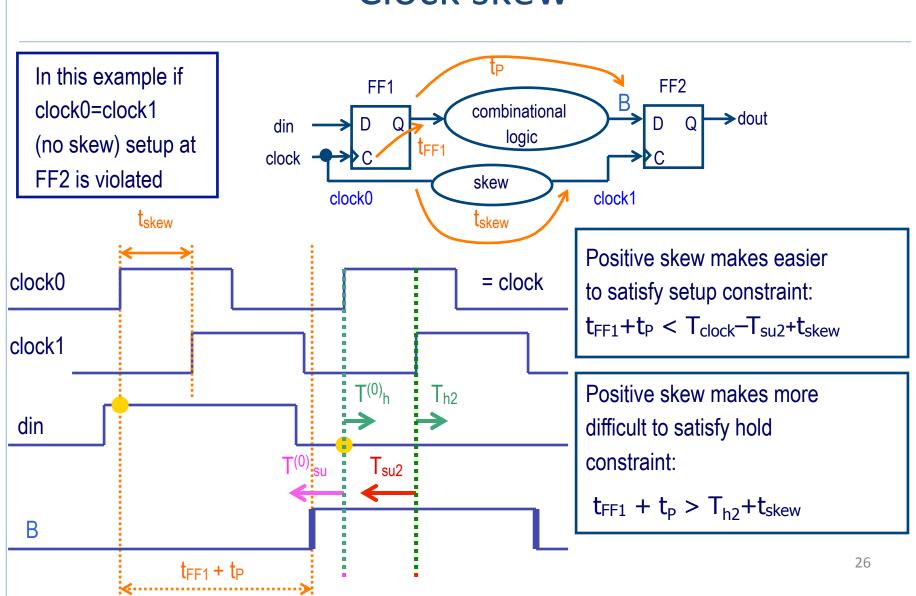

# Design Abstraction Levels

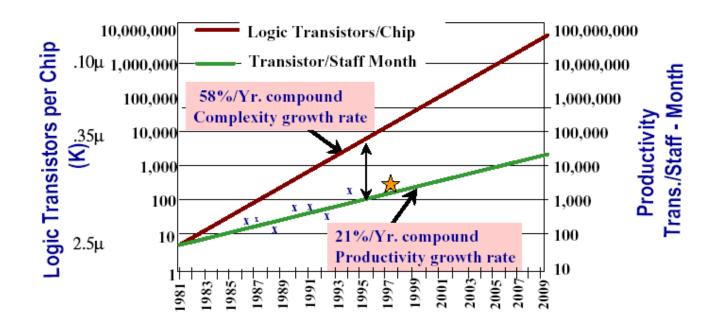

#### Moore's Law

- In 1963 Gordon Moore predicted that as a result of continuous miniaturization transistor count would double every 18 months

- 53% compound annual growth rate over 45 years

- No other technology has grown so fast so long

- Transistors become smaller, faster, consume less power, and are cheaper to manufacture

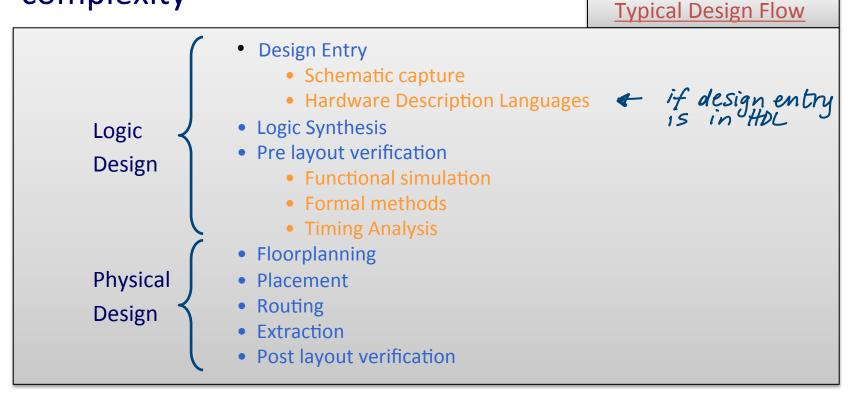

## The Design Productivity Gap

#### **CAD Tools**

Designers rely on design automation software tools to seek productivity gains and to cope with increased complexity

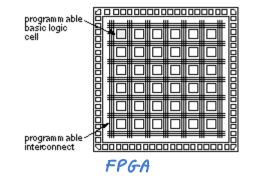

## Types of ICs Design Style

- \* Full-custom

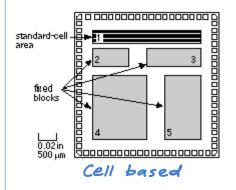

- \* Semi-custom

- Cell Based

- Gate Arrays

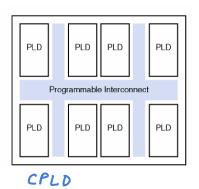

- \* Programmable

- CPLD and FPGA

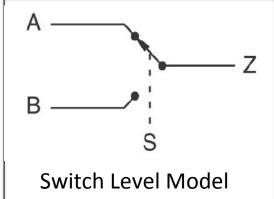

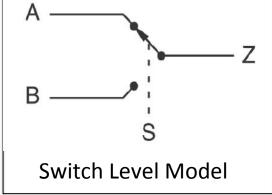

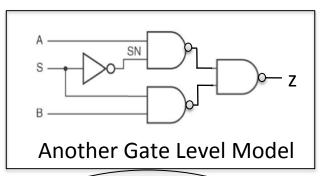

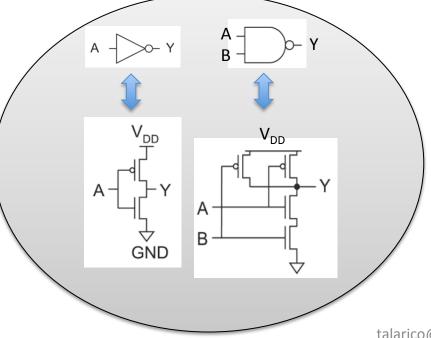

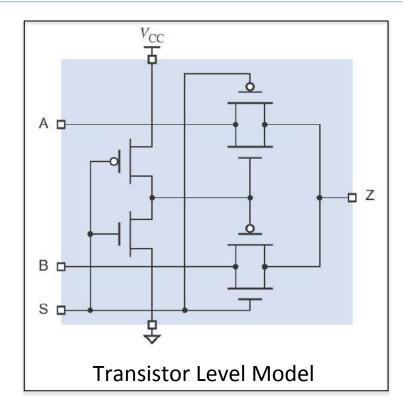

#### Back ... to Design Abstraction Levels

$$Z = A \cdot \bar{S} + B \cdot S$$

**Logic Equation**

#### **Truth Table**

| S | Α | В | Z |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 1 |

| 0 | 1 | 1 | 1 |

| 1 | 0 | 0 | 0 |

| 1 | 0 | 1 | 1 |

| 1 | 1 | 0 | 0 |

| 1 | 1 | 1 | 1 |

SB Gate Level Model

ASN

## ... Design Abstraction Levels

#### ... Design Abstraction Levels: HDL

```

library ieee;

use ieee.std logic 1164.all;

library altera;

use altera.altera primitives components.all;

entity mux is

port (A, B, S: in std logic;

out std logic);

end mux;

architecture struct of mux is

component INV is:

port A: in std logic;

F: out std logic);

end component;

component AND2 is:

port A, B: in std logic;

F: out std logic);

end component;

component OR2 is:

port A, B: in std logic;

F: out std logic);

end component;

```

signal SN, ASN, SB: std\_logic;

#### begin

U1: port map INV (S, SN); U2: port map AND2 (A, SN, ASN); U3: port map AND2 (S, B, SB); U4: port map OR2 (ASN, SB, Z);

end struct;

A ASN ASN SB SB SB

structural coding

- implement hierarchy

- infer "special" logic blocks (e.g. SRAM)

talarico@gonzaga.edu

#### ... Design Abstraction Levels: HDL

```

library ieee;

use ieee.std_logic_1164.all;

entity mux is

port (A, B, S: in std_logic;

Z: out std_logic);

end mux;

architecture rtl_conc of mux is

begin

Z <= A when S = '0' else B;

end rtl_conc;

```

concurrent RTL coding

**Preferred Style**

```

library ieee;

use ieee.std logic 1164.all;

entity mux is

port (A, B, S: in std logic;

Z:

out std logic);

end mux:

architecture rtl of mux is

begin

process mux p (A, B, S)

if (S = '0') then

Z \leq A:

else

Z <= B:

end if;

end process mux p;

end rtl;

```

sequential RTL coding