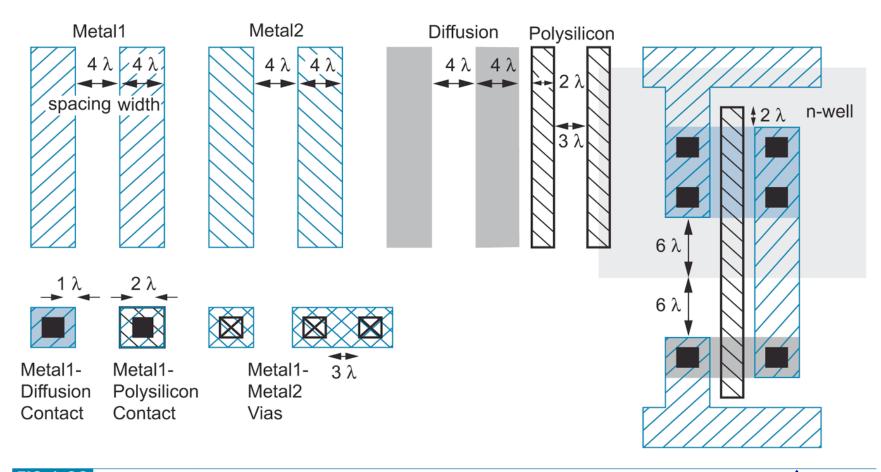

## Layout Design Rules

**FIG 1.39** Simplified  $\lambda$ -based design rules for layouts with 2-metal layers (MOSIS)

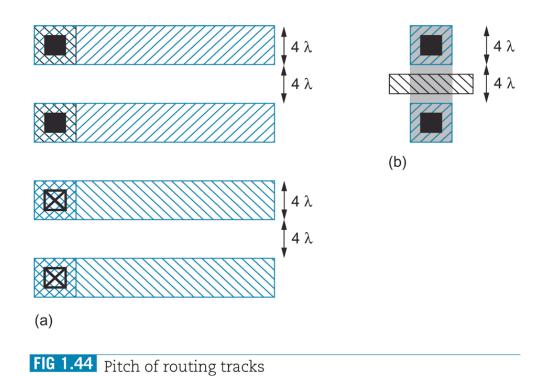

## Wiring Tracks

- A wiring track is the space required for a wire

- 4λ width, 4λ spacing from neighbor = 8λ pitch

- Transistors also consume one wiring track

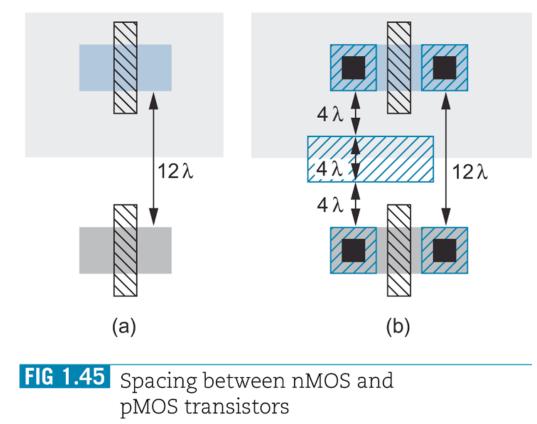

## Well Spacing

- Wells must surround transistors by 6λ

- Implies 12λ between opposite transistor flavors

- Leaves room for one wire track

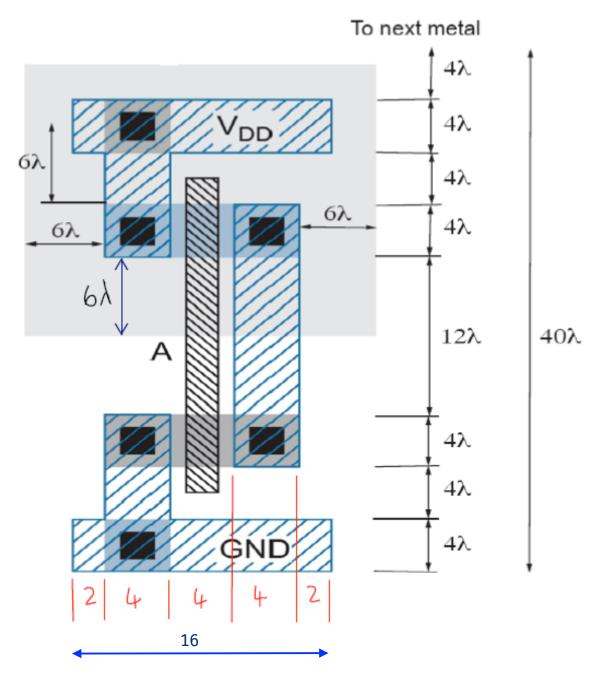

## **Inverter Standard Cell Area**

33