CPEN 230L: Introduction to Digital Logic lab.

Grading

The lowest score will be dropped

| Letter | Percentage |

| A | 100-94 |

| A– | 93-90 |

| B+ | 89-86 |

| B | 85-82 |

| B– | 81-78 |

| C+ | 77-74 |

| C | 73-70 |

| C– | 69-66 |

| D+ | 65-62 |

| D | 61-58 |

| F | 57-0 |

Assignments

Important documents to read thoroughly:

One stop link for the ICs datasheets needed for the class:

Free Tools

For PC users only: MobaXterm free Home edition (website)

Visual Studio Code or any other text editor you are already familiar with (including gedit, emacs, vi, notepad++, etc.)

Icarus Verilog (website)

GTKWave (website and documentation)

Check Icarus installation with this simple example:

//hello.v

module main;

initial

begin

$display("Hello, World");

$finish ;

end

endmodule

iverilog -o design hello.v vvp design

Hello, World

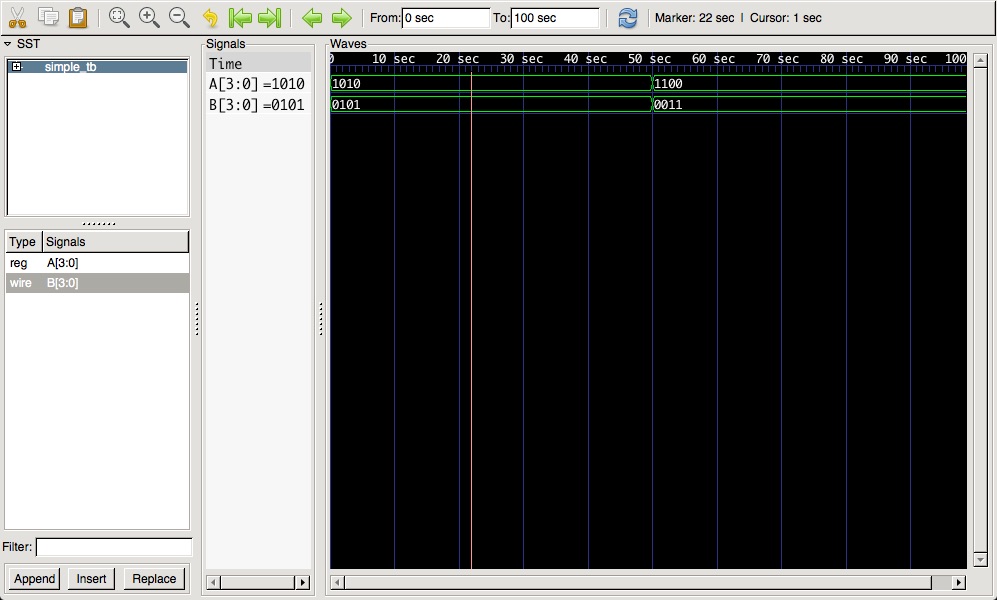

Check GTKWave installation with this simple example:

// file: simple.v

// flipping the input bits

module simple(A, B);

input [3:0] A;

output [3:0] B;

// mix up the input bits

assign B = { A[0], A[1], A[2], A[3] };

endmodule

// file: simple_tb.v

// check the functionality of simple.v is correct

`timescale 1ns / 1ns

module simple_tb;

reg [3:0] A = 4'b1010;

wire [3:0] B;

initial

begin

$dumpfile("simple.vcd");

$dumpvars(0);

$monitor("A is %b, B is %b.", A, B);

#50 A = 4'b1100;

#50 $finish;

end

simple dut(A, B);

endmodule

iverilog -o design simple.v simple_tb.v vvp design gtkwave simple.vcd

VCD info: dumpfile simple.vcd opened for output.

A is 1010, B is 0101.

A is 1100, B is 0011.

|

Commercial Tools

Quartus Prime (by Altera/Intel)

ModelSim (by Mentor Graphics)

A tutorial on how to use Quartus Prime and Modelsim with Verilog

Altera's original Tutorial (skip section 6 and section 7-2).

instead of section 6 of the original Tutorial please follow section “7: Simulation” of the condensed tutorialA condensed version of the Tutorial

A very terse summary of the Tutorial

RTL code (exor gate):

// File: light.v // A simple exor gate module light(x1,x2,f); input x1,x2; output f; assign f= (x1 & ~x2) | (~x1 & x2); endmodule

Testbench:

// File: light_tb.v

// Test Bench for the light module

// author: Claudio Talarico

`timescale 1ns / 1ns

module light_tb;

// inputs to DUT (RTL Hardware)

reg ain;

reg bin;

//outputs from DUT

wire cout;

// instantiate the DUT

light dut(

.x1( ain ),

.x2( bin ),

.f( cout )

);

// output the simulation in graphical format

initial

begin

$dumpfile("light.vcd");

$dumpvars(0);

end

//initialize inputs

initial

begin

ain = 0;

bin = 0;

end

// generate ain values

always

begin

# 20 ain = ~ain;

end

// generate bin values

always

begin

# 40 bin = ~bin;

end

// output the simulation in textual format

initial

begin

$monitor("At time %t, X1 is = %b, X2 is %b, F is %b",

$time, ain, bin, cout);

end

// stop the simulation from running forever

initial

begin

# 200 $stop;

end

endmodule

Pins Assignment:

# File: light.csv # Pin Assignments To, Direction, Location x1, input, PIN_AB28 x2, input, PIN_AC28 f, output, PIN_E21

or alternatively:

set_location_assignment PIN_AB28 -to x1 set_location_assignment PIN_AC28 -to x2 set_location_assignment PIN_E21 -to f

QuickStart on Verilog

A concise document on how to write good quality Verilog for synthesis by Cliff Cummings